Document ID: FLXU057

# FLEXIBILIS ETHERNET SWITCH (FES) FLEXIBILIS REDUNDANT SWITCH (FRS) Manual

# Revision History

| Rev                                                                       | Date       | Description                                                                                                                     |  |  |  |

|---------------------------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.0                                                                       | 13.6.2011  | First release.                                                                                                                  |  |  |  |

| 1.1                                                                       | 14.10.2011 | Minor improvements.                                                                                                             |  |  |  |

| 1.2                                                                       | 14.3.2012  | - HSR configuration register modified                                                                                           |  |  |  |

|                                                                           |            | - Configuration pins defined to give system clock frequency                                                                     |  |  |  |

|                                                                           |            | - PRP added                                                                                                                     |  |  |  |

|                                                                           |            | - HSR updates                                                                                                                   |  |  |  |

| 2.0                                                                       | 23.3.2012  | Approved                                                                                                                        |  |  |  |

| 2.1                                                                       | 1.6.2012   | HSR_CFG register clarifications (Table 11)                                                                                      |  |  |  |

| 2.2                                                                       | 11.6.2012  | Added IEEE 1588 Layer 2 functionality and Peer-to-peer transparent clock                                                        |  |  |  |

| 2.3 13.6.2012 Support for link local traffic without HSR tag or PRP trail |            |                                                                                                                                 |  |  |  |

|                                                                           |            | HSR_CFG register updates (Table 11)                                                                                             |  |  |  |

| 2.4                                                                       | 28.6.2012  | HSR_CFG register correction (Table 11)                                                                                          |  |  |  |

| 2.5                                                                       | 29.6.2012  | Changed PTP mode bits                                                                                                           |  |  |  |

| 2.6                                                                       | 15.8.2012  | Minor changes                                                                                                                   |  |  |  |

| 2.7                                                                       | 25.9.2012  | Clock interface changed.                                                                                                        |  |  |  |

| 2.8                                                                       | 14.12.2012 | Inbound Policy (IPO) registers changed.                                                                                         |  |  |  |

| 2.9                                                                       | 29.1.2013  | FES-HSR renamed to FRS                                                                                                          |  |  |  |

| 2.10                                                                      | 7.2.2013   | IP License Authentication added                                                                                                 |  |  |  |

| 2.11                                                                      | 18.4.2013  | Avalon interface, Ordinary/Boundary Clock support and host interrupts added.<br>Management mode now possible for all the ports. |  |  |  |

| 2.12                                                                      | 27.9.2013  | HSR/PRP Interlink support added. And up to four FRS instances can now share a single security chip.                             |  |  |  |

| 2.13 3.12.2013 New features:                                              |            | New features:                                                                                                                   |  |  |  |

|                                                                           |            | - Virtual LAN tagging and priority tagging                                                                                      |  |  |  |

| - MII clock enable signals                                                |            |                                                                                                                                 |  |  |  |

|                                                                           |            | - 12-port support (HSR_PORT_OPT 3)                                                                                              |  |  |  |

| 2.14                                                                      | 11.12.2013 | New counter registers                                                                                                           |  |  |  |

| 2.15                                                                      | 29.1.2014  | Added MAC address table read functionality and Time Trailer                                                                     |  |  |  |

| 2.16                                                                      | 22.4.2014  | New features:                                                                                                                   |  |  |  |

|                                                                           |            | Per port MAC table clear functionality                                                                                          |  |  |  |

|                                                                           |            | IPO match to source address                                                                                                     |  |  |  |

|                                                                           |            | Generics changed:<br>VLAN OPT removed                                                                                           |  |  |  |

|                                                                           |            | MGMT PORT OPT removed                                                                                                           |  |  |  |

|                                                                           |            | PORT STATE DEFAULT now 0x0120.                                                                                                  |  |  |  |

| 2.17                                                                      | 26.6.2014  | Document moved to a new updated document template. Register tables                                                              |  |  |  |

|                                                                           | 201012011  | changed from 16bit word addressing to byte addressing (just a documentation                                                     |  |  |  |

|                                                                           |            | change, no change in actual register locations).                                                                                |  |  |  |

| 2.18                                                                      | 10.9.2014  | New features:                                                                                                                   |  |  |  |

|                                                                           |            | Cut-Through between HSR redundant ports                                                                                         |  |  |  |

|                                                                           |            | Management Trailer length and bit offset now configurable                                                                       |  |  |  |

|                                                                           |            | Possibility to leave priority untouched in case of IPO match                                                                    |  |  |  |

|                                                                           |            | New generics:                                                                                                                   |  |  |  |

|                                                                           |            | CUT_THROUGH enable and disable                                                                                                  |  |  |  |

|                                                                           |            | COUNTERS enable and disable                                                                                                     |  |  |  |

| Rev  | Date      | Description                                                                                                                                                                                                                                                                                       |

|------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.19 | 18.6.2015 | HSR mode and management mode both allowed for a port at the same time.<br>Specified more precisely what happens in case of two IPO matches.<br>Added a warning about unnecessary clearing of the MAC address table.<br>Address lifetime configuration change                                      |

| 2.20 | 10.3.2016 | Added register settings for compensating TX and RX delay caused by PHYsical layer devices, interface adapters, SFP modules, etc.                                                                                                                                                                  |

| 3.0  | 30.6.2016 | FES (Flexibilis Ethernet Switch), FRS (Flexibilis Redundant Switch) and FDS (Flexibilis Deterministic Switch) integrated into the same document. Filename changed from FRS_Manual to FES_Manual. New licensing model, new generics, HSR mode X support, MACsec support and other smaller changes. |

| 3.1  | 8.12.2017 | Added register bit for enabling/disabling support for independent VLANs. (Bit 7 in GENERAL register)                                                                                                                                                                                              |

| 3.2  | 15.2.2021 | FDS (Flexibilis Deterministic Switch) removed from the document and related features added as optional features for FRS.                                                                                                                                                                          |

This document could contain technical inaccuracies or typographical errors. Flexibilis Oy may make changes in the product described in this document at any time.

Please, email comments about this document to support@flexibilis.com.

© Copyright Flexibilis Oy 2002-2017. All rights reserved.

Trademarks

All trademarks are the property of their respective owners.

# Contents

| 1 About This Document                                                | 9  |

|----------------------------------------------------------------------|----|

| 2 General Overview                                                   | 10 |

| 2.1 FES Features                                                     |    |

| 2.2 FRS                                                              |    |

| 2.2.1 Interface between MAC and PHY                                  |    |

| 2.2.2 Host System Interface                                          |    |

| 3 Introduction to Ethernet and Switching                             | 12 |

| 3.1 Ethernet Media Access Control (MAC)                              |    |

| 3.1.1 Preamble and Start Frame Delimiter (SFD)                       |    |

| 3.1.2 Header                                                         |    |

| 3.1.3 CRC                                                            |    |

| 3.1.4 Media Independent Interface (MII/GMII)                         |    |

| 3.2 Media Access Control (MAC) Bridge                                |    |

| 3.2.1 MAC Address Table                                              |    |

| 3.2.2 Shared Media versus Dedicated Media                            | 14 |

| 3.2.3 Cut-through versus Store-and-Forward Operation                 | 14 |

| 3.2.4 Spanning Tree Protocol                                         |    |

| 3.3 Precision Time Protocol                                          |    |

| 3.3.1 Transparent Clock                                              |    |

| 3.4 HSR (High-availability Seamless Redundancy)                      |    |

| 3.4.1 HSR Node Types                                                 |    |

| 3.5 Parallel Redundancy Protocol (PRP)                               |    |

| 3.5.1 PRP Node Types                                                 |    |

| 3.6 Traffic Shaping and Policing                                     |    |

| 3.7 Data Authenticity                                                |    |

| 4 Functional Description                                             |    |

| 4.1 Inbound Processing                                               | 24 |

| 4.1.1 RX MII                                                         |    |

| 4.1.2 Timestamp                                                      |    |

| 4.1.3 RX Pre-process                                                 |    |

| 4.1.4 MACsec                                                         |    |

| 4.1.5 Forwarding Decision                                            |    |

| 4.1.6 Inbound Policy                                                 |    |

| 4.1.7 Priority-setting                                               |    |

| 4.1.8 Traffic Policing                                               |    |

| 4.1.8.1 Default Policer                                              |    |

| 4.1.9 Precision Time Protocol                                        |    |

| 4.1.9.1 End-to-end Transparent Clock Functionality                   |    |

| 4.1.9.2 Peer-to-Peer Transparent Clock Support                       |    |

| 4.1.9.3 Ordinary and Boundary Clock Support                          |    |

| 4.1.9.3.1 Time Stamp Recording                                       |    |

| 4.1.9.3.2 Frame Modification                                         |    |

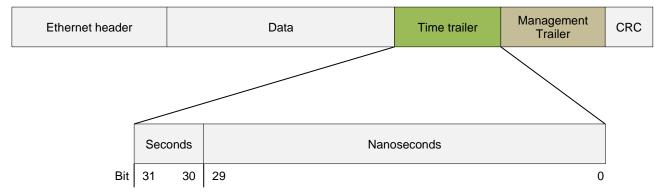

| 4.1.9.3.3 Time Trailer                                               |    |

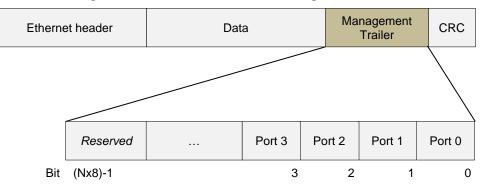

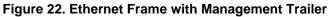

| 4.1.10 Management Trailer                                            |    |

| 4.1.10.1 Management Trailer with MACsec                              |    |

| 4.1.11 MAC Address Table                                             |    |

| 4.1.11.1 Dynamic MAC Address Table Entry                             |    |

| 4.1.11.2 Static MAC Address Table Entry<br>4.1.11.3 Address Learning |    |

| 4.1.11.3 Address Learning<br>4.1.11.4 Address Aging                  |    |

| 4.1.11.5 MAC Address and Forward Decision                            |    |

| 4.1.12 Virtual LANs (VLANs)                                          |    |

| 4.1.12 Villual LANS (VLANS)                                          |    |

| 4.2 Outbound Processing                                              |    |

|                                                                      |    |

| 4.2.1 TX Post-process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| 4.2.2 TX MII                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| 4.2.3 Timestamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| 4.2.4 MACsec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| 4.2.5 PTP Overwrite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                               |

| 4.3 Forwarding Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                               |

| 4.3.1 Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| 4.3.2 Priority Queues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                               |

| 4.3.2.1 Traffic Shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| 4.3.2.2 Configuring Shapers<br>4.3.3 Core RX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| 4.3.4 Core TX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

| 4.3.5 Frame Early Drop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

| 4.4 HSR (High-availability Seamless Redundancy)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| 4.4.1 Forwarding of HSR Frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| 4.4.2 HSR Port Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| 4.4.2.1 HSR Mode X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                               |

| 4.5 PRP (Parallel Redundancy Protocol)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

| 4.5.1 Forwarding of PRP Frames                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                               |

| 4.6 HSR/PRP interoperability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                               |

| 4.6.1 LanID, NetID and PathID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

| 4.7 IP License Authentication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                               |

| 4.8 Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               |

| 4.8.1 Software Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| 4.8.2 Hardware Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| 5 Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               |

| 5.1 FES Switch Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                               |

| 5.1 / ES Switch Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| 5.1.2 Frame Timestamp Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

| 5.1.3 Virtual LAN Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71                                                                                                            |

| 5.2 FES Port Configuration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                               |

| 5.2 FES Port Configuration Registers<br>5.2.1 General Configuration and State Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                                                                                                            |

| 5.2 FES Port Configuration Registers<br>5.2.1 General Configuration and State Registers<br>5.2.2 HSR/PRP Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>77                                                                                                      |

| 5.2 FES Port Configuration Registers<br>5.2.1 General Configuration and State Registers<br>5.2.2 HSR/PRP Registers<br>5.2.3 PTP Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>77<br>78                                                                                                |

| <ul> <li>5.2 FES Port Configuration Registers.</li> <li>5.2.1 General Configuration and State Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers.</li> <li>5.2.1 General Configuration and State Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers.</li> <li>5.2.1 General Configuration and State Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers.</li> <li>5.2.1 General Configuration and State Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71<br>77<br>78<br>79<br>89<br>92<br>92<br><b>96</b><br>98<br>99<br>99<br>99<br>100<br>101                     |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71<br>77<br>78<br>79<br>                                                                                      |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71<br>77<br>78<br>79<br>89<br>92<br><b>96</b><br>96<br>98<br>99<br>99<br>99<br>99<br>100<br>101<br>102<br>103 |

| 5.2 FES Port Configuration Registers.<br>5.2.1 General Configuration and State Registers<br>5.2.2 HSR/PRP Registers<br>5.2.3 PTP Registers<br>5.2.4 Counter Registers<br>5.2.5 Inbound Policy Registers.<br>5.2.6 MACsec Configuration Registers<br>5.2.6 MACsec Configuration Registers<br>6.1 Generics<br>6.2 General Signals<br>6.3 Avalon Slave Signals<br>6.3 Avalon Slave Signals<br>6.4 Time Interface Signals<br>6.5 Authentication Interface Signals<br>6.6 MII/GMII Signals<br>6.7 Speed Selection Signals<br>6.8 Transmit Clock Multiplexer<br>6.8.1 Interfacing to CPU with MII/GMII |                                                                                                               |

| <ul> <li>5.2 FES Port Configuration Registers</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                               |

| 5.2 FES Port Configuration Registers.<br>5.2.1 General Configuration and State Registers<br>5.2.2 HSR/PRP Registers<br>5.2.3 PTP Registers<br>5.2.4 Counter Registers<br>5.2.5 Inbound Policy Registers.<br>5.2.6 MACsec Configuration Registers<br>5.2.6 MACsec Configuration Registers<br>6.1 Generics<br>6.2 General Signals<br>6.3 Avalon Slave Signals<br>6.3 Avalon Slave Signals<br>6.4 Time Interface Signals<br>6.5 Authentication Interface Signals<br>6.6 MII/GMII Signals<br>6.7 Speed Selection Signals<br>6.8 Transmit Clock Multiplexer<br>6.8.1 Interfacing to CPU with MII/GMII |                                                                                                               |

# **Figures**

| Figure 1. FES Overview           | . 10 |

|----------------------------------|------|

| Figure 2. Ethernet Frame Formats |      |

| 5                                |      |

| Figure 3. HSR Ring Example with Unicast Message                    | 16  |

|--------------------------------------------------------------------|-----|

| Figure 4. HSR Ring Example with Multicast Message                  | 17  |

| Figure 5. HSR Tagged frame                                         | 17  |

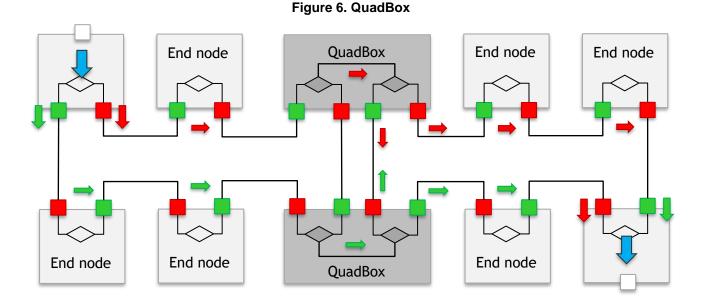

| Figure 6. QuadBox                                                  |     |

| Figure 7. PRP Double LAN                                           | 19  |

| Figure 8. PRP Frame                                                |     |

| Figure 9. MACsec Frame                                             |     |

| Figure 10. FES Block Diagram                                       |     |

| Figure 11. FES Forwarding Path                                     |     |

| Figure 12. FES Inbound and Outbound Processing Blocks              | 24  |

| Figure 13. Ethernet Frame Timestamp Point                          | 25  |

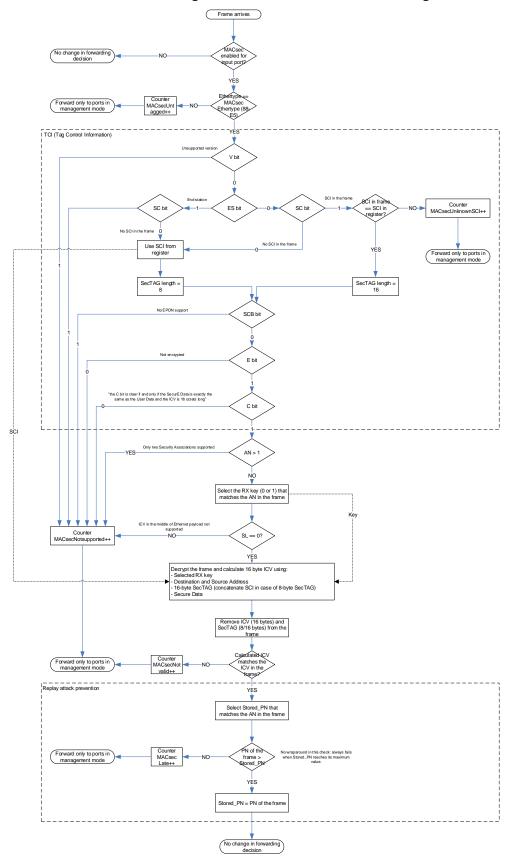

| Figure 14. MACsec Inbound Processing Block                         |     |

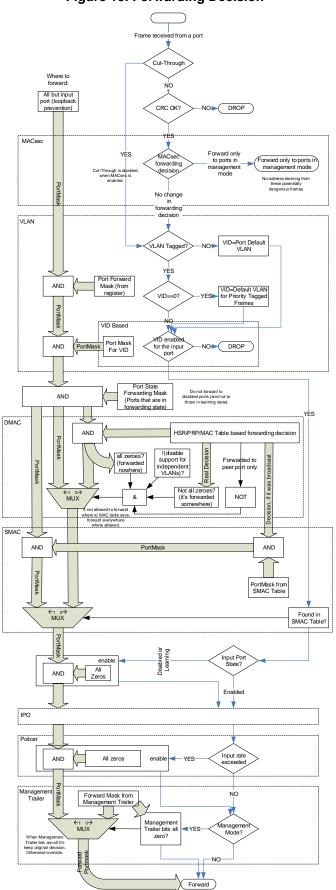

| Figure 15. Forwarding Decision                                     |     |

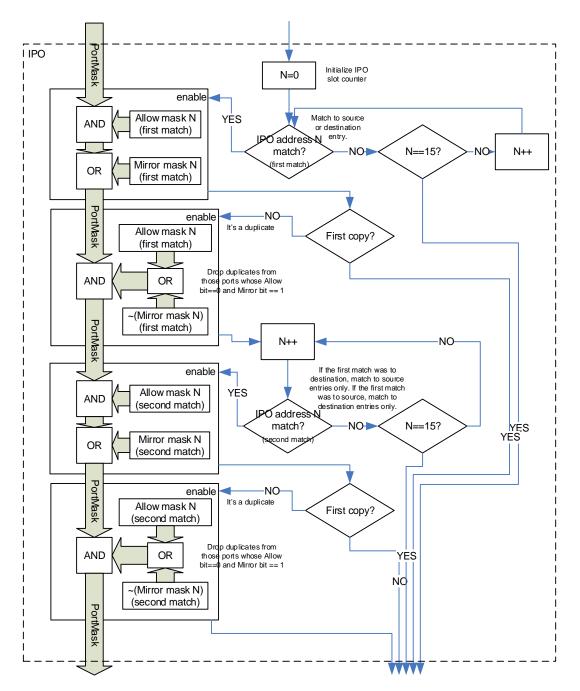

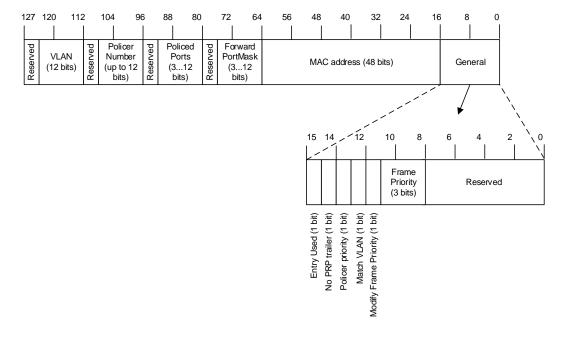

| Figure 16. Inbound Policy                                          |     |

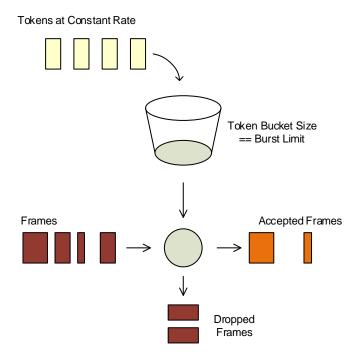

| Figure 17. Token Bucket Principle                                  | 32  |

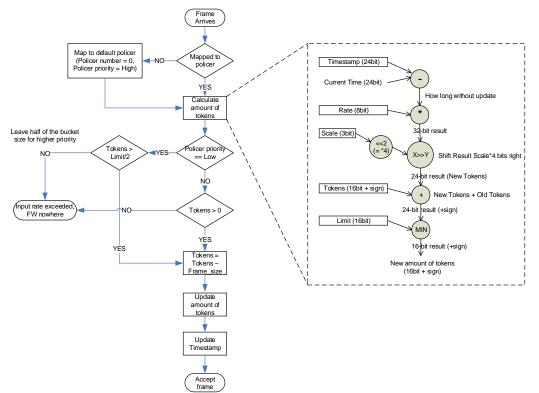

| Figure 18. Token Bucket Operation for Frames                       |     |

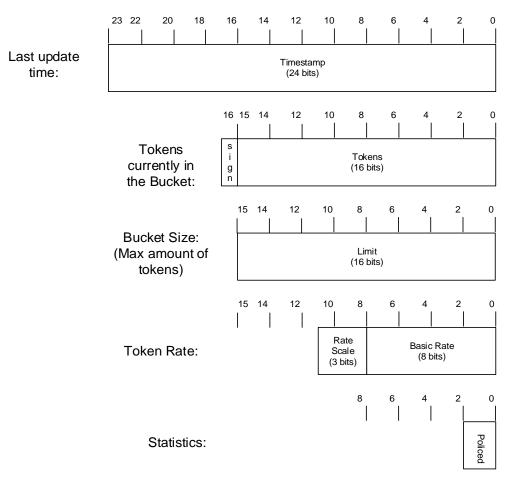

| Figure 19. Data Stored for each Token Bucket                       |     |

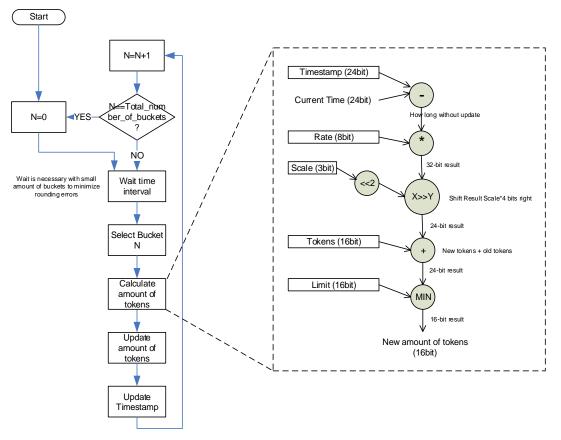

| Figure 20. Bucket Update Background Process                        |     |

| Figure 21. Ethernet Frame with Time Trailer                        | 37  |

| Figure 22. Ethernet Frame with Management Trailer                  | 37  |

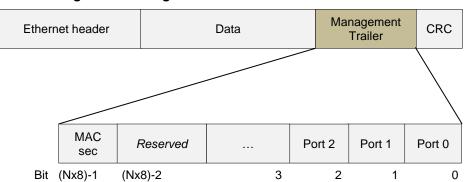

| Figure 23. Management Trailer with 3-port FES and 8-bit offset     | 38  |

| Figure 24. Management Trailer when MACsec enabled                  |     |

| Figure 25. MAC Address Entry                                       |     |

| Figure 26. Static MAC Address Entry                                |     |

| Figure 27. Static MAC Address Table                                | 40  |

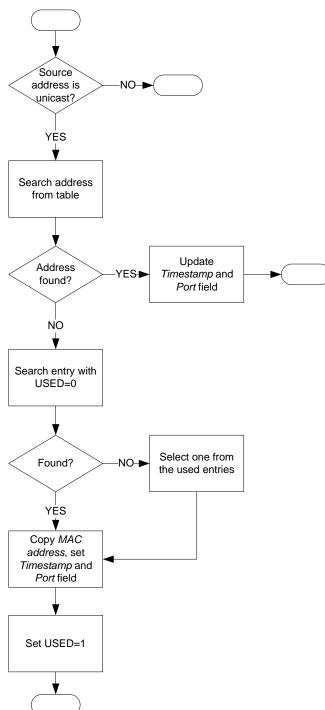

| Figure 28. Address Learning                                        |     |

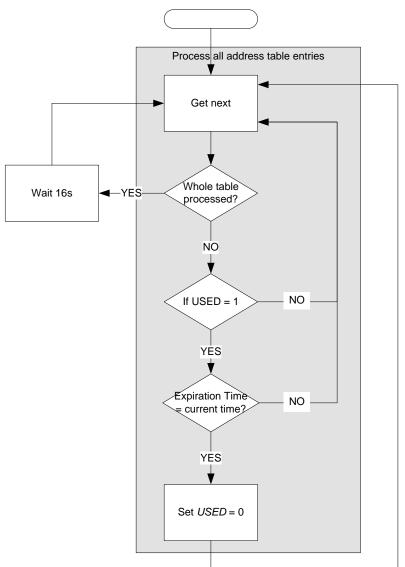

| Figure 29. Address Aging                                           |     |

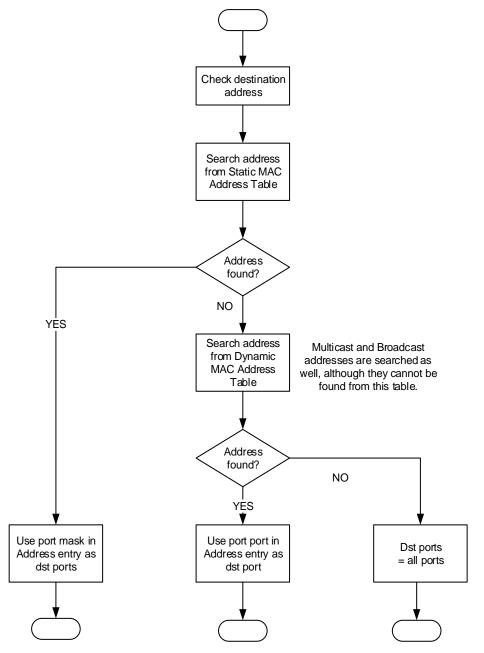

| Figure 30. MAC Address Search & Forwarding Decision                |     |

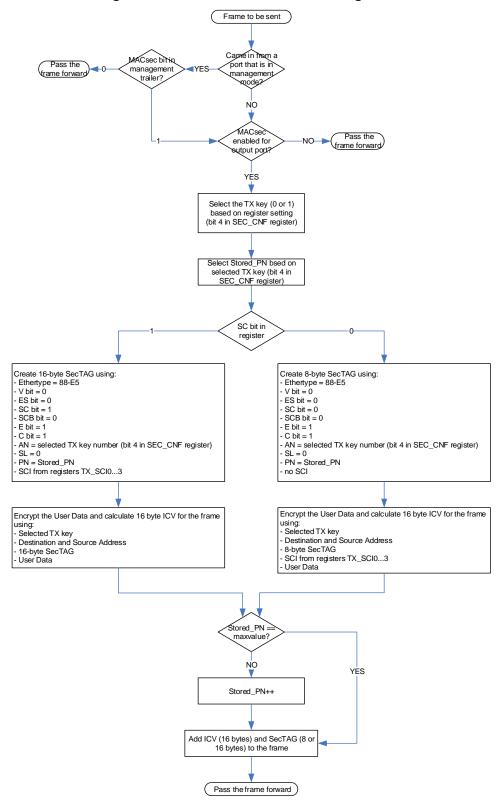

| Figure 31. MACsec Outbound Processing block                        |     |

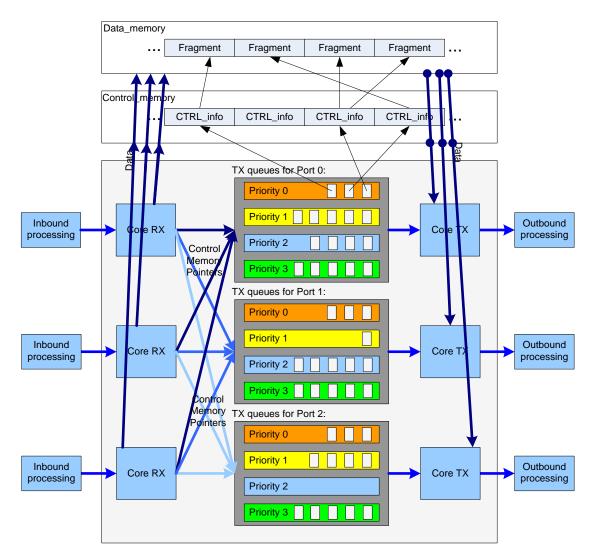

| Figure 32. Priority Queues (only three ports shown)                |     |

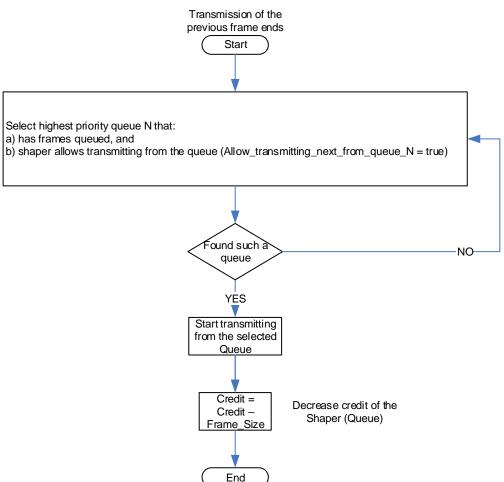

| Figure 33. Selection of Transmit Queue                             |     |

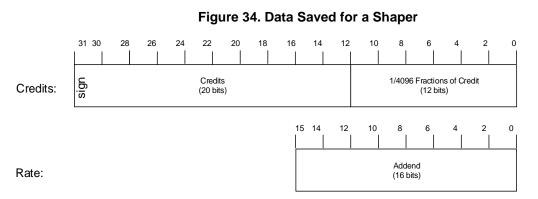

| Figure 34. Data Saved for a Shaper                                 |     |

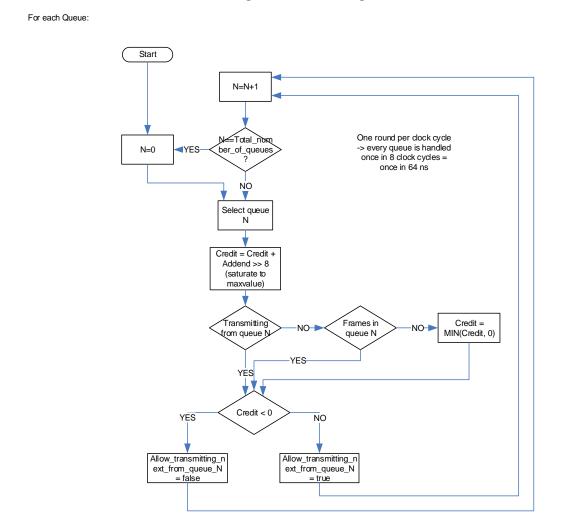

| Figure 35. Increasing of Credit                                    |     |

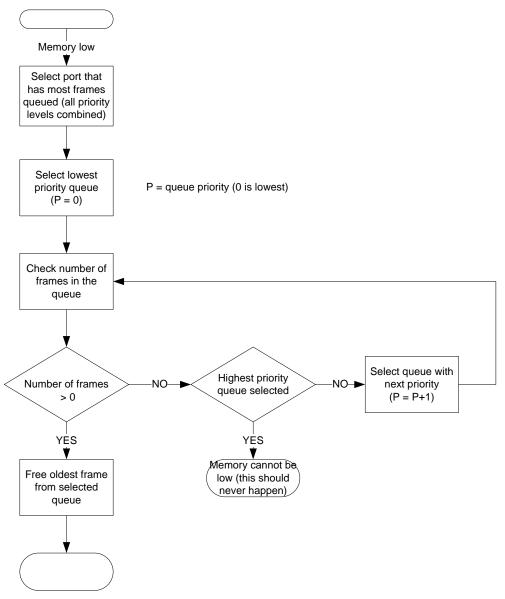

| Figure 36. Frame Early Drop Algorithm                              |     |

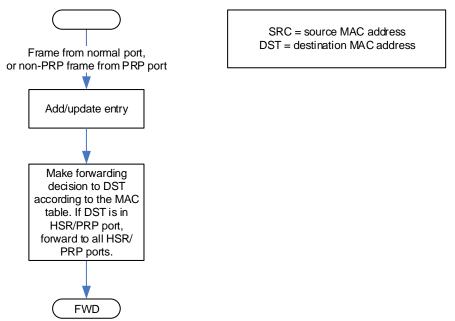

| Figure 37. Frame from normal port (or non-PRP frame from PRP port) |     |

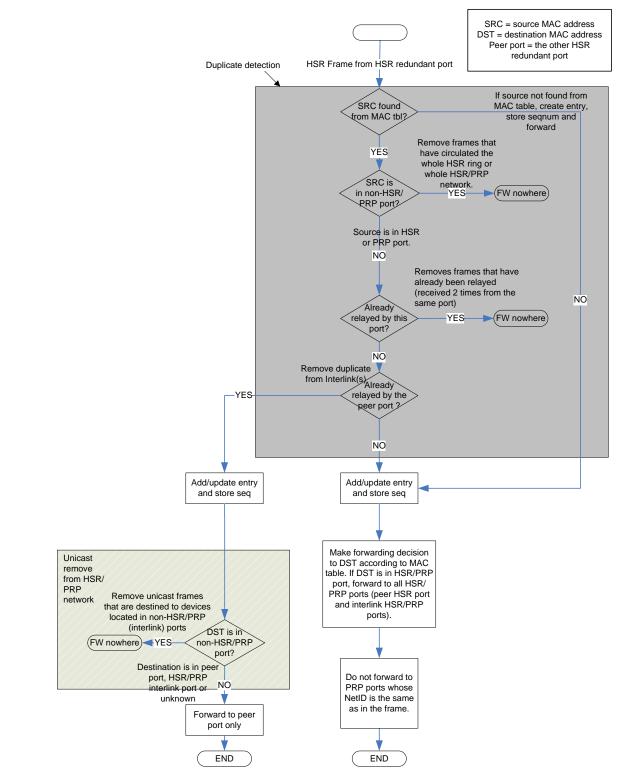

| Figure 38. HSR Redundant Port Forwarding Logic                     |     |

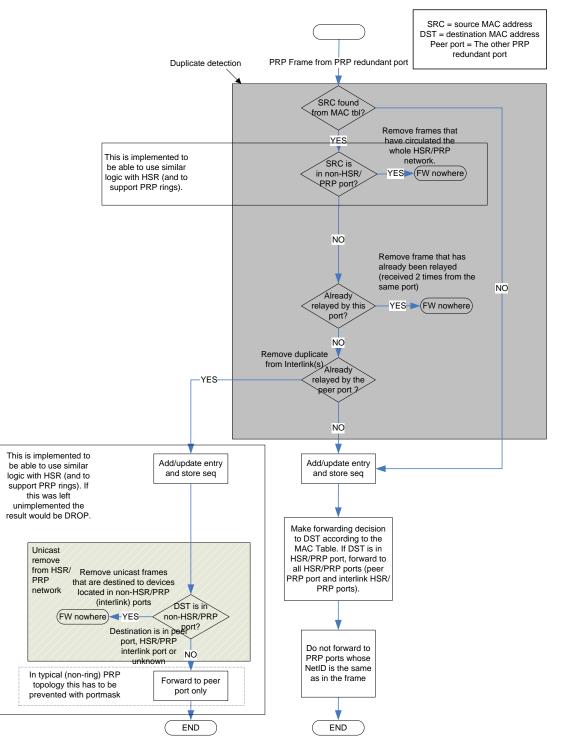

| Figure 39. PRP Redundant Port Forwarding Logic                     |     |

| Figure 40. External Signals of FES                                 | 96  |

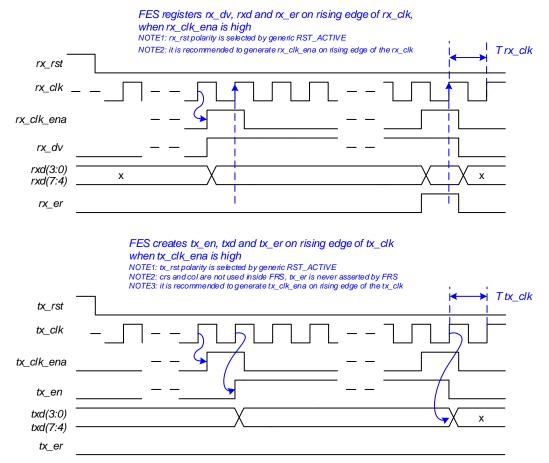

| Figure 41. (G)MII signal timing for signal port                    | 101 |

| Figure 42. External Transmit Clock Multiplexer                     |     |

| Figure 43. Host Interface Connection                               |     |

| Figure 44. Authentication Interface Multiplexer                    | 108 |

# **Tables**

| Table 1. Features of FES and FRS                           | 11 |

|------------------------------------------------------------|----|

| Table 2. Definition of LanID, NetId, ring NetId and PathId | 56 |

| Table 3. Resulting LanId and NetId                         | 56 |

| Table 4. FES Example Register Map                          | 58 |

| Table 5. FES Switch Configuration Register Groups          | 58 |

| Table 6. General Switch Configuration Registers            | 59 |

| Table 7. Frame Timestamp Registers                         |    |

| Table 8. Virtual LAN Configuration Registers               | 70 |

| Table 9. FES Port Configuration Register Groups            | 71 |

| Table 10. General Configuration and State Registers        |    |

| Table 11. HSR Registers                                    |    |

| Table 12. PTP Registers                                    | 78 |

| -                                                          |    |

| Table 13. Counter Registers                | 80  |

|--------------------------------------------|-----|

| Table 14. Inbound Policy Registers         | 90  |

| Table 15. MACsec Configuration Registers   |     |

| Table 16. FES Generics                     |     |

| Table 17. General Signals                  |     |

| Table 18. Avalon Slave Signals             |     |

| Table 19. Time Interface Signals           | 100 |

| Table 20. MII/GMII Signals                 | 101 |

| Table 21. Speed Selection Signals          | 102 |

| Table 22. MII/GMII Clock Mux Configuration | 104 |

# **1 About This Document**

This document describes Flexibilis Ethernet Switch (FES). Flexibilis Redundant Switch (FRS) is FES with redundant networking features. FES is an Ethernet switch Intellectual Property (IP) core targeted at programmable hardware platforms. It is also possible to integrate FES into an ASIC. FES is written in VHDL language.

This document is targeted for current and potential users of FES. This includes those who are designing software employing the functions of FES, and those who are evaluating the usability of FES in their system or project. This documentation is not targeted at those who want to make changes in the implementation of FES, and therefore this document does not cover detailed information about the internal implementation of FES. The internal implementation details are documented in Flexibilis Ethernet Switch/Router Specification [1]. FPGA tools and their usage is also out of the scope of this document.

Chapter 2 gives a general overview of FES: what it is, what can be done with it, and what are the main features of it. Chapter 3 contains a short introduction to Ethernet and switching in general and chapter 4 describes FES functionality in more detail. Chapter 5 defines the register map of FES and Chapter 6 defines the external signals. Chapter 7 contains a glossary and chapter 8 contains the references.

In this document signal names are written in *signal\_name* style. Block names are written with Capital first letter. Pseudo code is written in PseudoCode style and command line commands are written in CommandLine style. References are marked in the document in [brackets].

# 2 General Overview

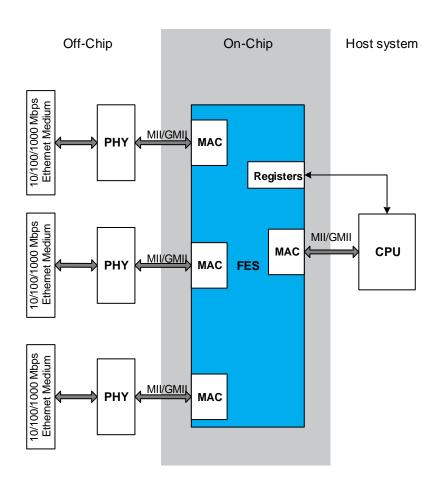

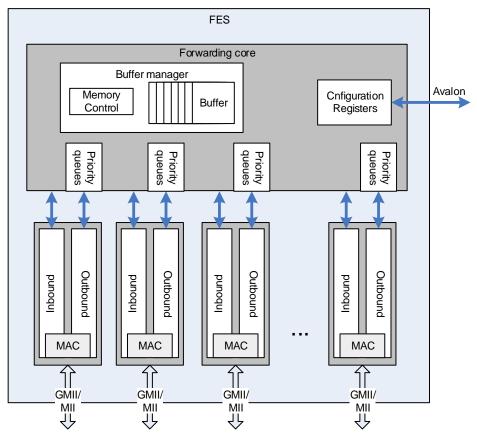

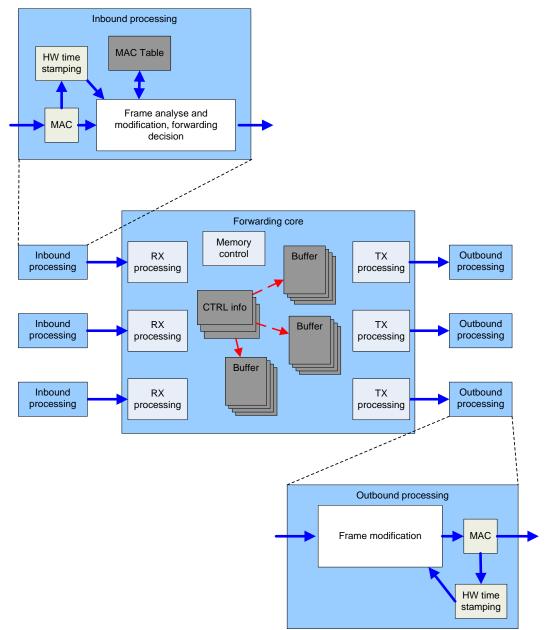

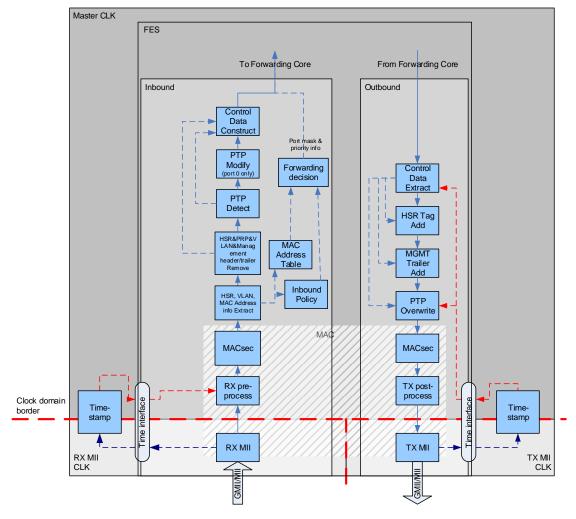

FES is an Ethernet switch IP block designed to be used in programmable environments. FES includes multiple Ethernet Media Access Controller (MAC) functional entities and provides MII/GMII interfaces for Ethernet PHY devices and optionally for a host system CPU (see Figure 1).

#### Figure 1. FES Overview

# 2.1 FES Features

FES standard and optional features include:

- 10/100/1000 Mbit/s Full-Duplex Ethernet interfaces (IEEE 802.3x [2])

- Compatible with IEEE standard 802.1D Media Access Control (MAC) Bridges [3]

- Ethernet packet forwarding at wire-speed, non-blocking

- Media Independent Interfaces (MII) and Gigabit Media Independent Interfaces (GMII) for attaching to external Physical Layer devices (PHY) and host system CPU. Other interface types including SGMII, RGMII, RMII, 1000BASE-X and 100BASE-FX can be provided with optional interface adapters on the FPGA [4]

- Avalon slave interface for register access

- PTPv2 end-to-end one-step transparent clock [5] processing at hardware

- PTPv2 peer-to-peer transparent clock [5] support functions

- PTPv2 boundary and ordinary clock [5] support functions

- Ethernet packet filtering and prioritization on each of the ports

- Compatible with IEC 62439-3 "High-availability Seamless Redundancy (HSR)"

- Compatible with IEC 62439-3 "Parallel Redundancy Protocol (PRP)"

- Virtual LAN tagging and priority tagging

- Traffic shaping and policing

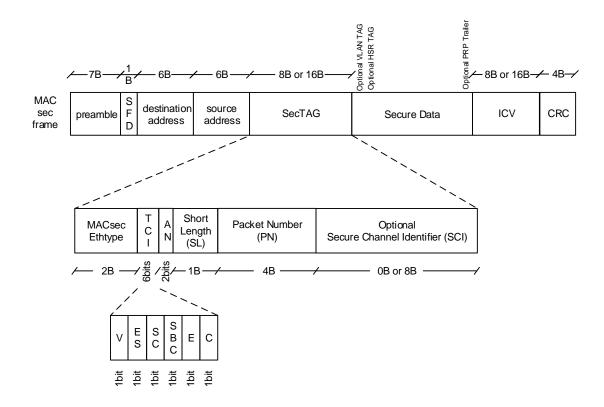

- Frame encryption and decryption with MACsec

# **2.2 FRS**

FES with features for redundant communication is called Flexibilis Redundant Switch (FRS). FRS is targeted for applications requiring high availability. The standard and optional features of FES and FRS are listed in Table 1. Optional features need to be licensed separately.

| Feature:                 | FES | FRS |

|--------------------------|-----|-----|

|                          |     |     |

| Ethernet switch          | х   | x   |

| Number of ports*         | 312 | 38  |

| Priority Queues per port | 4   | 4   |

| IEEE 1588                | Х   | x   |

| HSR                      | -   | x   |

| PRP                      | -   | x   |

| Static MAC table         | -   | 0   |

| Traffic Policing         | -   | 0   |

| Traffic Shaping          | -   | 0   |

| MACsec                   | -   | 0   |

| Table 1 | Features  | of FES | and FRS |

|---------|-----------|--------|---------|

|         | i caluico |        | anuino  |

"x" = standard, "o" = optional, "-" = not available

\* When redundancy (HSR/PRP) is enabled, the maximum port count is 8. Otherwise the maximum port count is 12.

It is possible to adjust the selected feature set during product development by licensing optional features and/or adjusting the generics (Table 16).

#### 2.2.1 Interface between MAC and PHY

FES supports Media Independent Interface (MII) and Gigabit Media Independent Interface (GMII). GMII is used only when an Ethernet port is in 1000 Mbps operating mode. In 10 Mbps and 100 Mbps operating modes FES uses MII interface.

GMII interface contains more signals than MII interface, for example receive and transmit data paths are four bits wider. The signals that exist in both GMII interface and MII interface share the same signals in FES.

Reduced pin count interfaces (RMII and RGMII) are supported by using external to FES RMII and RGMII adapter blocks at the FPGA. Serial SGMII interfaces are supported with SGMII adapters, and for connecting to fiber optic transceivers there are 100BASE-FX and 1000BASE-X adapters. The available Ethernet interface adapters are described in a separate document [4].

#### 2.2.2 Host System Interface

FES has a special feature in its Ethernet interfaces that is helpful when the interface is connected to a host system CPU. This feature of FES is called management mode. By using the management mode it is possible for the CPU to send/receive packets to/from any other port independent from the MAC address table and other configurations.

# 3 Introduction to Ethernet and Switching

This chapter contains an introduction to Ethernet, Ethernet switching, Precision Time Protocol (IEEE 1588v2) and High-availability Seamless Redundancy (HSR).

# 3.1 Ethernet Media Access Control (MAC)

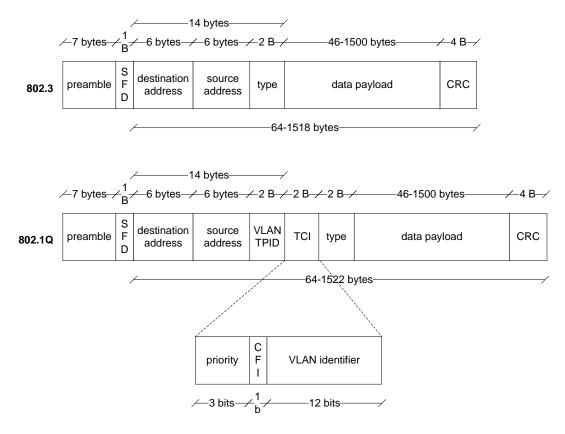

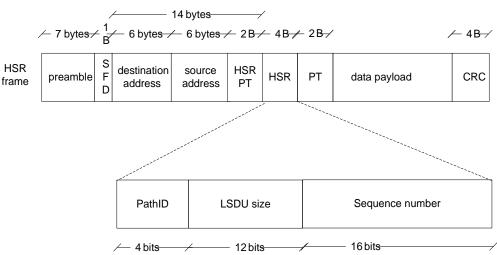

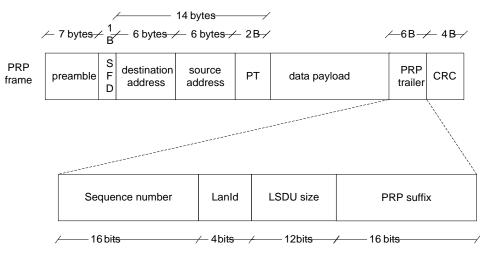

The Media Access Control (MAC) protocol is used to provide the data link layer of Ethernet protocol. The MAC protocol encapsulates data by adding a 14 byte header before the payload and a 32 bit Cyclic Redundancy Check (CRC) checksum after the payload. In addition to this, there is a 7 byte preamble and a 1 byte Start Frame Delimiter (SFD) before the header, see Figure 2.

In case of Virtual LAN (VLAN) tagging being used, the header is 4 bytes longer because of an additional type field and a VLAN tag. This also increases the Ethernet frame's maximum length from 1518 bytes to 1522 bytes (without preamble and SFD). This means that an Ethernet Bridge should support forwarding of up to at least 1522 byte frames.

Figure 2. Ethernet Frame Formats

## 3.1.1 Preamble and Start Frame Delimiter (SFD)

Between every frame, there is a small idle time called an Interframe Gap. The length of the Interframe Gap is 96 bits. After an Interframe Gap a node starts its transmission by sending a preamble sequence consisting of 56 alternating 1's and 0's. The purpose of the preamble sequence is to synchronize the receiver(s) before the actual data arrives. After the preamble comes a Start Frame Delimiter ("0x5D") that indicates the starting point of the actual frame (the header).

#### 3.1.2 Header

MAC header consists of three parts:

Destination Address field (6 bytes)

The Destination Address specifies whether the recipient is a single node (unicast), a group of nodes

reibicis Trech industrial

(multicast), or all the nodes at the medium (broadcast). If the first bit is zero, then the recipient is a single node and this field contains the physical address of the receiver's interface.

- Source address field (6 bytes) The physical address of the interface that originated the frame.

- Type/Length field (2 bytes) The type field indicates the protocol being carried. In the case of IEEE 802.3 LLC, this field can also be used to indicate the length of the data. If the value of the field is less than or equal to 1500, then it is indicating the length of the frame.

Ethernet nodes are usually capable of choosing whether they want to receive only frames sent to their own Ethernet address and the broadcast address, or also frames sent to some, or all of the multicast addresses. The nodes may also choose to receive all the frames, including those destined for other nodes. This is called promiscuous mode.

## 3.1.3 CRC

The 32-bit cyclic redundancy check (CRC) checksum at the end of the frame provides an error detection mechanism. The CRC checksum is calculated and added to the frame when the frame is sent, and it is checked when the frame is received at the opposite end. Frames received with an invalid CRC checksum contain an error and should be discarded by the receiver.

## 3.1.4 Media Independent Interface (MII/GMII)

Media Independent Interface (MII) is a standardized interface between MAC and PHY. MII interface can exist in different forms, it can for example be a physical connector between two devices or it can be just signals between two devices on a circuit board. It is also possible that a MII interface exists inside a single chip, between two functional blocks. The idea of the MII interface is that it is independent of the physical medium. In practise this means that the same Ethernet MAC can be used with various kinds of Ethernet media. The MII interface standard supports both 10 Mbps and 100 Mbps transfer rates. For gigabit media there is GMII (Gigabit Medium Independent Interface).

# 3.2 Media Access Control (MAC) Bridge

MAC Bridges allow communications between end stations attached to separate LANs (network segments). A bridge has an own separate MAC for each LAN it connects to and it is able to bridge traffic between the LANs transparent to logical link control (LLC) and network layer protocols, just as if the stations were attached to the same LAN. MAC Bridges with more than two ports are commonly called as switching hubs or Ethernet switches.

Functional entities of an Ethernet switch can be divided roughly into three parts: Forwarding Process, Address Learning Process and MAC address table (forwarding database). The Forwarding Process forwards Ethernet frames between the ports according to MAC address table updated by the Address Learning Process. The Address Learning Process observes all the received frames and learns which stations are in which network segments by storing their MAC addresses into the MAC address table.

Ethernet frames whose destination is known by the switch to be in the network segment behind another port are forwarded into that port. If the destination is known to be behind the same port where from the frame was received, the switch discards the frame. Ethernet frames whose destination is unknown (the address is not yet stored into the MAC address table, or the address information is deleted from the MAC address table because of being too old) are forwarded to every other port than the source port. Also frames with broadcast (and multicast) destination addresses are forwarded by switches to every other port that the source port as they are supposed to reach every station in the network.

## 3.2.1 MAC Address Table

The operations on the MAC address table can be broke down to three different processes; a learning process, a lookup process and an aging process.

The learning process compares the source addresses of the received frames to the addresses in the MAC address table. If the entry is found to be already in the table, the port mapping information is updated if it has changed (the network topology has changed), and the entry is refreshed so that the aging process does not

remove it prematurely. If the address entry cannot be found from the table, it is added there. If the table is already full it may be necessary to remove some other entry from the table. Note that if the network topology changes and nodes are moved from a switch port to another, the switch will not have correct information on the whereabouts of the node until it transmits something or the aging process removes the entry. Until then frames destined to the node will be forwarded to wrong port and they will never reach their destination.

The lookup process compares the destination addresses of the received frames to the addresses in the MAC address table. According to this information the forwarding process either discards the frame or forwards it to another or to all other ports. Note that frames are never forwarded to the port where from they were received, as that would cause duplicate frames to the network.

The aging process removes entries from the MAC address table. The entries are removed when they have not been refreshed by the learning process for some time. In many switches this aging time is configurable, but not always, in which case the default value of 5 minutes is typically used. The aging process helps to keep the MAC address table small, which may in some cases affect the time taken by address lookup (depends on the search algorithm used). The other reason for aging process to exist is to be able to react to network topology changes in case there are nodes that do not transmit too often or nodes that do not initiate any communication by themselves.

## 3.2.2 Shared Media versus Dedicated Media

"There are no shared-medium implementations of Ethernet at data rates above 10Mb/s." [6]

Unfortunately still today many Ethernet tutorials present Ethernet as a shared medium despite the fact that typical Ethernet network has not been a shared medium for a decade. Shared Ethernet, where technologies like Carrier Sense Multiple Access (CSMA) and Collision Detection (CD) are used in gaining access to the physical medium, is today legacy technology. Today's Ethernet is switched, which means that every end node has a dedicated port in an Ethernet switch. In switched Ethernet every network segment consists of an end-node, an Ethernet switch and a point-to-point link between them.

Switched Ethernet has many advantages over a shared media:

- Full-Duplex links offer double the capacity of a Half-Duplex link at the same nominal speed

- Different nodes are able to operate with different data rates

- Network capacity is used more efficiently and latency minimized as all the frames are not forwarded to all the nodes and links

- Full-Duplex operation allows links to be longer in distance because CSMA/CD protocol does not limit the maximum length. Today fiber optic Ethernet links can have range of over 100 kilometres.

#### 3.2.3 Cut-through versus Store-and-Forward Operation

According to the IEEE standard 802.1D "Media Access (MAC) Bridges" [3] every port of the MAC bridge has an individual MAC entity examining all the frames transmitted to the medium by the other node(s). The CRC checksums of the received frames are checked by calculating CRC of the received frames and comparing it to the CRC checksum at the end of the frame. Frames with erroneous CRC checksums should be silently discarded.

The so called cut-through switches that start to forward the frame before it is fully received, do not conform with the standard in this respect, because they are not able to discard the received frames if they have an erroneous CRC checksum. The opposite of cut-through operation is store-and-forward operation, in which case frames are fully received and their CRC checksums are checked before they are forwarded. This is standard compliant method of operation.

## 3.2.4 Spanning Tree Protocol

Spanning Tree Protocol (STP) is a protocol that automatically removes loops from a switched Ethernet network. A loop-free topology is achieved by disabling some of the network links, to form a tree topology from the mesh topology. Loop-free topology is needed, because if there was a loop in the network Ethernet frames would circulate in the loop for infinite time.

According to the standard (IEEE 802.1D) the Spanning Tree Protocol configures full, simple, and symmetric connectivity throughout a Bridged Local Area Network that comprises individual LANs interconnected by Bridges. The Spanning Tree Protocol (STP) configures the Port State of each Bridge Port in the Bridged Local

Area Network. STP ensures that the stable connectivity provided by each Bridge between its Ports and by the individual LANs to which those Ports attach is predictable, manageable, full, simple, and symmetric. STP further ensures that temporary loops in the active topology do not occur if the network has to reconfigure in response to the failure, removal, or addition of a network component, and that erroneous station location information is removed from the Filtering Database after reconfiguration.[3]

STP and its improved version Rapid Spanning Tree Protocol (RSTP)[7] use configuration messages sent to a specific multicast MAC address to create and maintain the network topology. In addition to the STP protocol stack, support for STP requires the Bridge to support certain port states (Disabled, Learning and Forwarding) and capture the STP configuration messages for the STP protocol stack.

# **3.3 Precision Time Protocol**

Precision Time Protocol (PTP), defined in IEEE standard 1588 [5], is a protocol enabling precise synchronization of device clocks in packet based networks, for example Ethernet. Devices running PTP are automatically synchronized to the most accurate clock in the network. The protocol supports system wide synchronization accuracy in sub microsecond range with minimal network and local clock computing resources. It is used for example by test and measurement, power-line management, industrial automation and telecom applications.

PTP accuracy is based on an assumption that the delay in Ethernet is approximately constant and symmetric. Because of the packet based traffic in Ethernet, Ethernet switches in the path of the packets cause variable delay for packet throughput, thus degrading PTP synchronization accuracy. Transparent PTP clock functionality removes these problems and enables precise synchronization of clocks in switched Ethernet.

## 3.3.1 Transparent Clock

Transparent Clock timestamps PTP event frames in receive and in transmission ports and calculates the delay caused by the switch by subtracting the receive timestamp from the transmission timestamp. In PTP end-to-end transparent one step switch, the calculated delay is added to the correction field of the PTP event frame. A PTP slave that receives the PTP event message corrects the delay calculation by removing the effect of the PTP transparent clocks by subtracting the correction field value from the calculated total packet transmission delay. PTP peer-to-peer transparent clock measures the delay of the ingress path and includes that also in the correction field value.

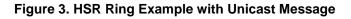

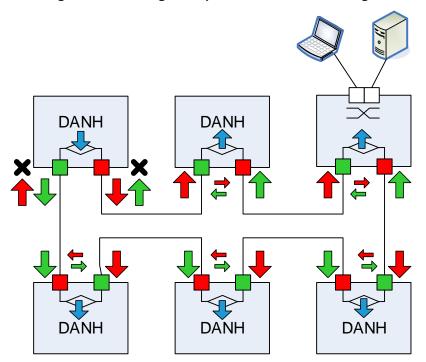

# 3.4 HSR (High-availability Seamless Redundancy)

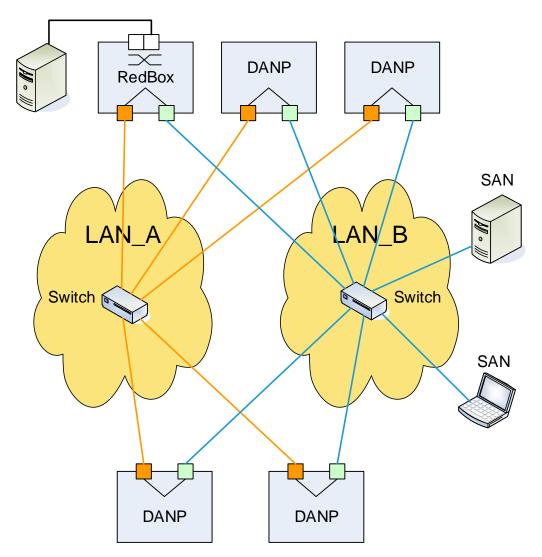

Standard IEC62439-3 [9] deals with redundancy in Ethernet networks. The HSR concept introduces network ring(s), where each possible source and destination pair is always connected via two routes. In case of a fault, the ring breaks, but still provides connection between source and destination(s) via second path, as shown in Figure 3 and Figure 4. HSR can also be used with double LAN topology as depicted in Figure 7 (if SANs are attached directly to LAN A or LAN B, they need to have HSR support). The standard is developed for demanding and mission-critical applications such as substation automation.

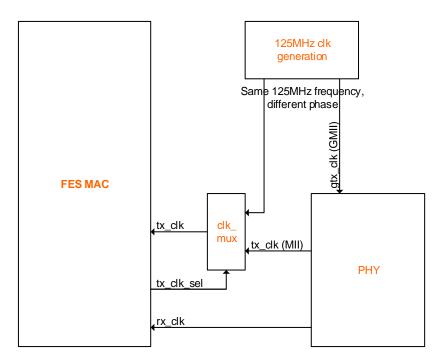

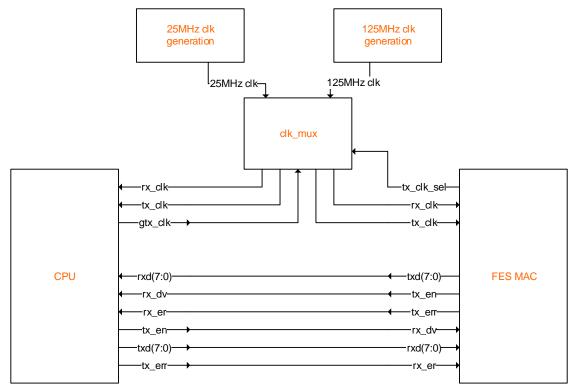

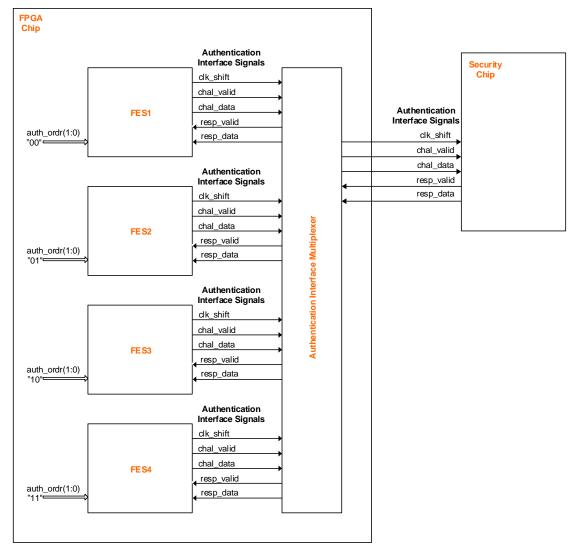

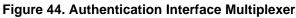

Figure 4. HSR Ring Example with Multicast Message