# SpeedChip XRS7000 and XRS3000 Series

# **User Manual**

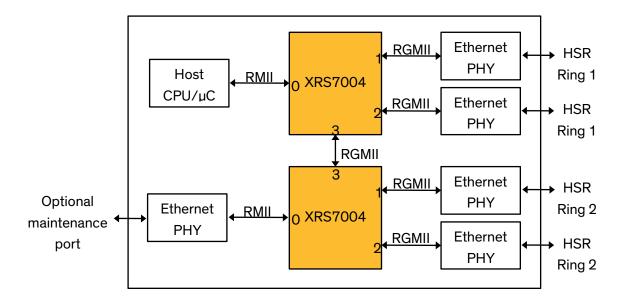

The XRS7004, XRS7003 and XRS3003 are HSR and PRP (IEC 62439-3 Clause 5 & 4) enabled singlechip gigabit Ethernet switches. XRS7003 and XRS3003 can be employed in HSR and PRP Endnodes and XRS7004 in both End-Nodes and HSR and PRP RedBoxes. A QuadBox can be built using two XRS7004 devices.

## Features

- 144-pin Plastic Enhanced Quad Flat Pack (EQFP) (22mm x 22mm, 0.5 mm pitch) or 256-pin Fine Ball Grid Array (FBGA) Package (17mm x 17mm, 1.0 mm ball pitch)

- Industrial Temperature Range -40°C to +100°C

- Two (XRS7003, XRS3003) or three (XRS7004) 10/100/1000 Mbit/s Full-Duplex Ethernet interfaces (RGMII)

- 10/100 Mbit CPU port (RMII)

- Gigabit wire speed forwarding capacity, nonblocking

- I2C and MDIO interfaces for register access (only MDIO in XRS3003)

- Cut-through and Store-and-Forward operation

- Quality of Services (QoS) with four priority queues per port

- Per port packet filtering

- VLAN tagging (not in XRS3003)

- Priority tagging (not in XRS3003)

- IEEE 1588 Precision Time Protocol (PTP) support with internal Real-Time Clock (RTC)

- HW counters for implementing Remote Network MONitoring (RMON) SNMP MIB (not in XRS3003)

- Support for MAC address based authentication methods

- Support for Spanning Tree Protocol (STP) and Rapid Spanning Tree Protocol (RSTP) implementations

- PPS (Pulse per Second) input and output (only output in XRS3003)

## High-availability Seamless Redundancy and Parallel Redundancy Protocol

HSR and PRP protocols are used in applications that require short reaction time and high availability. Typical applications include smart grid electrical substation automation and other critical networking applications such as industrial automation, motion control, vehicle and military communication. HSR and PRP provide a network that has no single point of failure and zero recovery time in case of a failure: Single network faults will not result in any frame loss. The network is fully operational even during maintenance as any network device can be disconnected and replaced without breaking the network connectivity.

XRS7000 and XRS3000 User Manual, Version 1.3

/ **Five Years** Out

**Table 1. Device Features**

| Feature                                        | XRS7004E               | XRS7004F               | XRS7003E               | XRS7003F               | XRS3003F           |

|------------------------------------------------|------------------------|------------------------|------------------------|------------------------|--------------------|

| 10/100/1000 Mbit/s<br>RGMII ports              | 3                      | 3                      | 2                      | 2                      | 2                  |

| 10/100 Mbit/s RMII ports                       | 1                      | 1                      | 1                      | 1                      | 1                  |

| High-Availability Seamless<br>Redundancy (HSR) | Yes                    | Yes                    | Yes                    | Yes                    | Yes                |

| Parallel Redundancy<br>Protocol (PRP)          | Yes                    | Yes                    | Yes                    | Yes                    | Yes                |

| Precision Time Protocol<br>(PTP)               | Yes                    | Yes                    | Yes                    | Yes                    | Yes                |

| Register Access                                | MDIO, I <sup>2</sup> C | MDIO only          |

| Queues per port                                | 4                      | 4                      | 4                      | 4                      | 4                  |

| Maximum number of VLANs                        | 4096                   | 4096                   | 4096                   | 4096                   | No VLAN<br>support |

| Recommended HSR<br>network size                | Up to 512<br>hops      | Up to 512<br>hops      | Up to 512<br>hops      | Up to 512<br>hops      | Up to 512<br>hops  |

| HSR proxy node table size                      | 512 MAC<br>Addresses   | 512 MAC<br>Addresses   | 64 MAC<br>Addresses    | 64 MAC<br>Addresses    | 1 MAC<br>Address   |

| Package                                        | EQFP144                | FBGA256                | EQFP144                | FBGA256                | FBGA256            |

| Operating Junction<br>Temperature range        | -40°C to<br>+100°C     | -40°C to<br>+100°C     | -40°C to<br>+100°C     | -40°C to<br>+100°C     | -40°C to<br>+100°C |

XRS7000 and XRS3000 User Manual, Version 1.3

# Contents

| 1. | CONVENTIONS USED IN THIS DOCUMENT |                                                                          |    |  |  |

|----|-----------------------------------|--------------------------------------------------------------------------|----|--|--|

| 2. | TYP                               | PICAL APPLICATIONS                                                       | 9  |  |  |

| 3. | PIN                               | DESCRIPTION                                                              | 11 |  |  |

|    | 3.1                               | EQFP144 Package                                                          |    |  |  |

|    | 3.2                               | FBGA256 Package                                                          |    |  |  |

| 4. | FUN                               | NCTIONAL OVERVIEW                                                        |    |  |  |

| 5. | REG                               | GISTER INTERFACE                                                         |    |  |  |

|    | 5.1                               | Device Identification Registers                                          |    |  |  |

|    | 5.2                               | MDIO Slave                                                               |    |  |  |

|    | 5.3                               | I2C Slave                                                                |    |  |  |

|    | 5.4                               | MDIO and I2C Slave Address Configuration                                 |    |  |  |

| 6. | RED                               | DUNDANT SWITCH (RS)                                                      |    |  |  |

|    | 6.1                               | Inbound Processing                                                       |    |  |  |

|    |                                   | 6.1.1 RX MII                                                             |    |  |  |

|    |                                   | 6.1.2 Timestamp                                                          |    |  |  |

|    |                                   | 6.1.3 RX Pre-process<br>6.1.4 Forwarding Decision                        |    |  |  |

|    |                                   | <ul><li>6.1.4 Forwarding Decision</li><li>6.1.5 Inbound Policy</li></ul> |    |  |  |

|    |                                   | 6.1.6 Priority-setting                                                   |    |  |  |

|    |                                   | 6.1.7 Precision Time Protocol                                            |    |  |  |

|    |                                   | 6.1.8 Management Trailer                                                 |    |  |  |

|    |                                   | 6.1.9 MAC Address Table                                                  |    |  |  |

|    |                                   | 6.1.10 Virtual LANs (VLANs)                                              | 54 |  |  |

|    |                                   | 6.1.11 Forward Portmask                                                  | 55 |  |  |

|    | 6.2                               | Outbound Processing                                                      |    |  |  |

|    |                                   | 6.2.1 TX Post-process                                                    |    |  |  |

|    |                                   | 6.2.2 TX MII                                                             |    |  |  |

|    |                                   | 6.2.3 Timestamp                                                          |    |  |  |

|    |                                   | 6.2.4 PTP Overwrite                                                      |    |  |  |

|    | 6.3                               | Forwarding Core                                                          |    |  |  |

|    |                                   | 6.3.1 Memory Controller                                                  |    |  |  |

|    |                                   | 6.3.2 Priority Queues                                                    |    |  |  |

|    |                                   | 6.3.3 Frame Early Drop                                                   |    |  |  |

|    | 6.4                               | HSR (High-availability Seamless Redundancy)                              |    |  |  |

|    |                                   | 6.4.1 Forwarding of HSR Frames                                           |    |  |  |

|    |                                   | 6.4.2 HSR Port Modes                                                     | 61 |  |  |

|    | 6.5                               | PRP (Parallel Redundancy Protocol)                                       |    |  |  |

|    |                                   | 6.5.1 Forwarding of PRP Frames                                           |    |  |  |

|    | 6.6                               | HSR/PRP interoperability                                                 |    |  |  |

|    | 6.7                               | Allowed Port Modes                                                       |    |  |  |

|    | 6.8                               | Software Reset                                                           |    |  |  |

|    | 6.9                               | Switch Configuration Registers                                           |    |  |  |

|    |                                   | 6.9.1 General Switch Configuration Registers                             |    |  |  |

|    |                                   | 6.9.2 Frame Timestamp Registers                                          |    |  |  |

|    |                                   | 6.9.3 Virtual LAN Configuration Registers                                |    |  |  |

XRS7000 and XRS3000 User Manual, Version 1.3

V Five Years Out

| 6.10.1       General Configuration and State Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 6.10 Port Configuration Registers                |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------|-----|

| 6.10.3       PTP Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 6.10.1 General Configuration and State Registers |     |

| 6.10.4       Counter Registers       90         6.10.5       Inbound Policy Registers       103         7.       REAL-TIME CLOCK (RTC)       107         7.1       Registers       107         8.       TIME STAMPER (TS)       112         8.1       Registers       112         9.       GENERAL-PURPOSE IO (GPIO)       116         9.1       Registers       116         9.1       Registers       116         10.2       Recommended Operating Conditions       120         10.1       Absolute Maximum Ratings       120         10.2       Recommended Operating Conditions       120         10.3       Package Thermal Information       121         10.4       DC Electrical Characteristics       122         10.4.1       Current consumption       122         10.4.2       I/O Characteristics       123         10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       124         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       IQC Timing       126         10.5.6       MDIO Timing       126                                                                         |     | 6.10.2 HSR/PRP Registers                         |     |

| 6.10.5       Inbound Policy Registers       103         7. REAL-TIME CLOCK (RTC)       107         7.1       Registers       107         8. TIME STAMPER (TS)       112         8.1       Registers       112         9. GENERAL-PURPOSE IO (GPIO)       116         9.1       Registers       116         9.1       Registers       116         10.2       Recommended Operating Conditions       120         10.3       Package Thermal Information       120         10.4       DC Electrical Characteristics       122         10.4.1       Current consumption       122         10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       123         10.5.2       Reset Timing       124         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.6       MDIO Timing       129         11.1       ECPF144 Package       130         11.1       ECPF144 Package       130         11.1       ECPF144 Package       130         11.1       ECPF144 Package       130         11.1.1       ECPF144 Package       130 <td></td> <td>6.10.3 PTP Registers</td> <td></td>                           |     | 6.10.3 PTP Registers                             |     |

| 7. REAL-TIME CLOCK (RTC)       107         7.1 Registers       107         8. TIME STAMPER (TS)       112         8.1 Registers       112         9. GENERAL-PURPOSE IO (GPIO)       116         9. I. Registers       116         9. I. Registers       116         10. ELECTRICAL SPECIFICATION       120         10.1 Absolute Maximum Ratings       120         10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.5.2 Reset Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       125         10.5.4 RMII Timing       126         10.5.5 INDUCTION       128         10.5.6 MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1 EOFP144 Package       130         11.1 EOFP144 Package       130         11.1 EOFP144 Package       132         12. ORDERING INFORMATION       134                                                                                                       |     | 6.10.4 Counter Registers                         |     |

| 7.1       Registers       107         8.       TIME STAMPER (TS)       112         8.       1       Registers       112         9.       GENERAL-PURPOSE IO (GPIO)       116       112         9.       GENERAL-PURPOSE IO (GPIO)       116         9.1       Registers       116         10. ELECTRICAL SPECIFICATION       120         10.1       Absolute Maximum Ratings       120         10.2       Recommended Operating Conditions       120         10.3       Package Thermal Information       121         10.4       DC Electrical Characteristics       122         10.4.1       Current consumption       122         10.4.2       I/O Characteristics       123         10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       123         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       IC Timing       126         10.5.6       MDIO Timing       129         11.       MCCHANICAL SPECIFICATION       130         11.1       EOFP144 Package       130         11.1       EOFP144 Package       130 </th <th></th> <th>6.10.5 Inbound Policy Registers</th> <th></th> |     | 6.10.5 Inbound Policy Registers                  |     |

| 8. TIME STAMPER (TS)       112         8.1 Registers       112         9. GENERAL-PURPOSE IO (GPIO)       116         9.1 Registers       120         10.1 Absolute Maximum Ratings       120         10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       126         10.5.4 RMII Timing       126         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11.1 EQFP144 Package       130         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERIN                                                           | 7.  | . REAL-TIME CLOCK (RTC)                          |     |

| 8.1       Registers.       112         9.       GENERAL-PURPOSE IO (GPIO)       116         9.1       Registers       116         9.1       Registers       116         10.       ELECTRICAL SPECIFICATION       120         10.1       Absolute Maximum Ratings       120         10.2       Recommended Operating Conditions       120         10.3       Package Thermal Information       121         10.4       DC Electrical Characteristics       122         10.4.1       Current consumption       122         10.4.2       I/O Characteristics       123         10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       123         10.5.3       RGMII Timing       124         10.5.4       RMII Timing       126         10.5.5       I2C Timing       126         10.5.6       MDIO Timing       129         11.       MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.1       EQFP144 Package       132         12.       ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                          |     | 7.1 Registers                                    |     |

| 9. GENERAL-PURPOSE IO (GPIO)       116         9.1 Registers       116         9.1 Registers       116         10. ELECTRICAL SPECIFICATION       120         10.1 Absolute Maximum Ratings       120         10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       123         10.5.4 RMII Timing       126         10.5.5 I/2C Timing       128         10.5.6 MDIO Timing       128         10.5.6 MDIO Timing       129         11.1 EOFP144 Package       130         11.1 EOFP144 Package       130         11.1 EOFP144 Package       132         12. ORDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                    | 8.  | . TIME STAMPER (TS)                              |     |

| 9.1       Registers.       116         10. ELECTRICAL SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 8.1 Registers                                    | 112 |

| 10. ELECTRICAL SPECIFICATION       120         10.1 Absolute Maximum Ratings       120         10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       125         10.5.4 RMII Timing       126         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1 EOFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                      | 9.  | . GENERAL-PURPOSE IO (GPIO)                      |     |

| 10.1 Absolute Maximum Ratings       120         10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       123         10.5.3 RGMII Timing       124         10.5.4 RMII Timing       125         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12.0 ORDERING INFORMATION       134                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 9.1 Registers                                    | 116 |

| 10.2 Recommended Operating Conditions       120         10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       125         10.5.4 RMII Timing       126         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERING INFORMATION       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10  | 0. ELECTRICAL SPECIFICATION                      |     |

| 10.3 Package Thermal Information       121         10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       125         10.5.4 RMII Timing       126         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11.1 EOFP144 Package       130         11.2 FBGA256 Package       132         12.0 ROBERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 10.1 Absolute Maximum Ratings                    |     |

| 10.4 DC Electrical Characteristics       122         10.4.1 Current consumption       122         10.4.2 I/O Characteristics       123         10.5 Interface Timing       123         10.5.1 Input Clock Timing       123         10.5.2 Reset Timing       124         10.5.3 RGMII Timing       125         10.5.4 RMII Timing       126         10.5.5 I2C Timing       128         10.5.6 MDIO Timing       129         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12.0 RDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 10.2 Recommended Operating Conditions            |     |

| 10.4.1       Current consumption       122         10.4.2       I/O Characteristics       123         10.5       Interface Timing       123         10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       123         10.5.3       RGMII Timing       124         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12.0       RDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 10.3 Package Thermal Information                 | 121 |

| 10.4.2       I/O Characteristics       123         10.5       Interface Timing.       123         10.5.1       Input Clock Timing.       123         10.5.2       Reset Timing.       124         10.5.3       RGMII Timing.       125         10.5.4       RMII Timing.       126         10.5.5       I2C Timing.       128         10.5.6       MDIO Timing.       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package.       130         11.2       FBGA256 Package.       132         12. ORDERING INFORMATION.       134         12.1       Part Ordering Numbers.       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 10.4 DC Electrical Characteristics               |     |

| 10.5       Interface Timing.       123         10.5.1       Input Clock Timing.       123         10.5.2       Reset Timing.       124         10.5.3       RGMII Timing.       125         10.5.4       RMII Timing.       126         10.5.5       I2C Timing.       128         10.5.6       MDIO Timing.       129         11.       MECHANICAL SPECIFICATION.       130         11.1       EOFP144 Package.       130         11.2       FBGA256 Package.       132         12.       ORDERING INFORMATION.       134         12.1       Part Ordering Numbers.       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 10.4.1 Current consumption                       |     |

| 10.5.1       Input Clock Timing       123         10.5.2       Reset Timing       124         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11.       MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12.       ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 10.4.2 I/O Characteristics                       |     |

| 10.5.2       Reset Timing       124         10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | 10.5 Interface Timing                            |     |

| 10.5.3       RGMII Timing       125         10.5.4       RMII Timing       126         10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 10.5.1 Input Clock Timing                        |     |

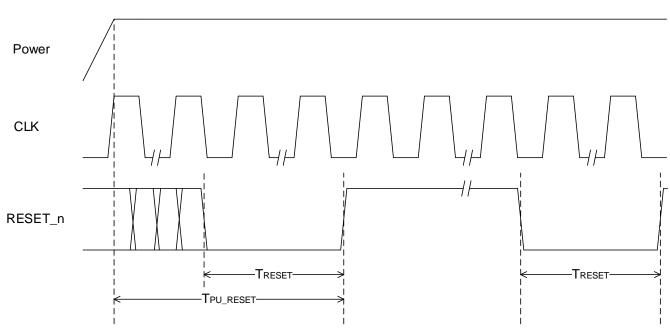

| 10.5.4       RMII Timing       126         10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 10.5.2 Reset Timing                              |     |

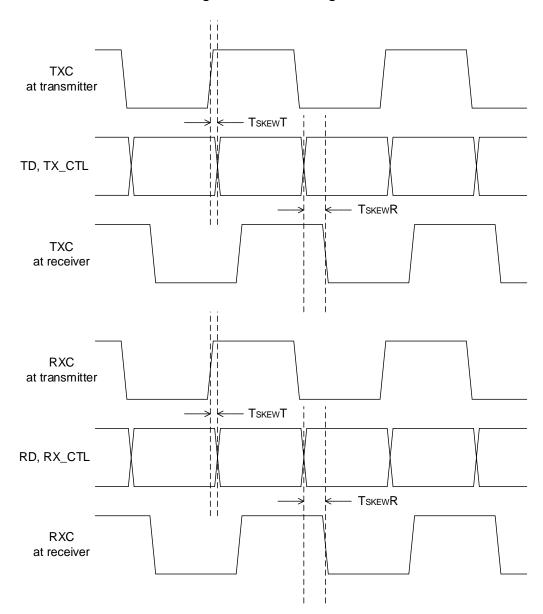

| 10.5.5       I2C Timing       128         10.5.6       MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1       EQFP144 Package       130         11.2       FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1       Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 10.5.3 RGMII Timing                              |     |

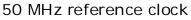

| 10.5.6 MDIO Timing       129         11. MECHANICAL SPECIFICATION       130         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | 10.5.4 RMII Timing                               |     |

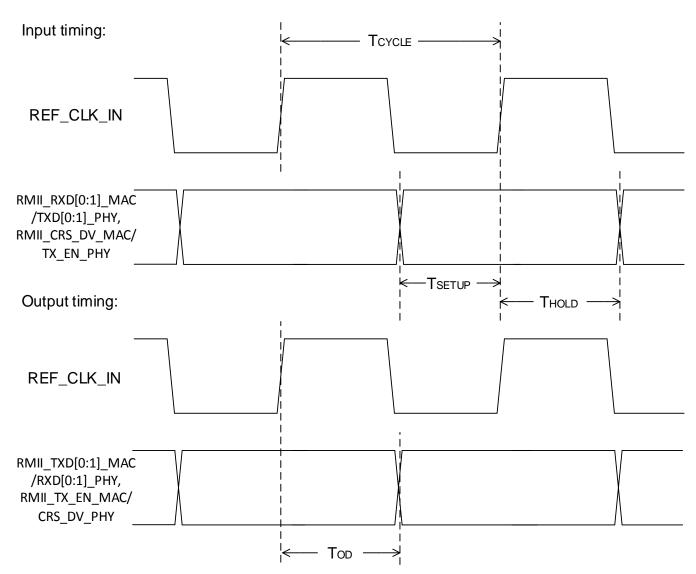

| 11. MECHANICAL SPECIFICATION       130         11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | 10.5.5 I2C Timing                                |     |

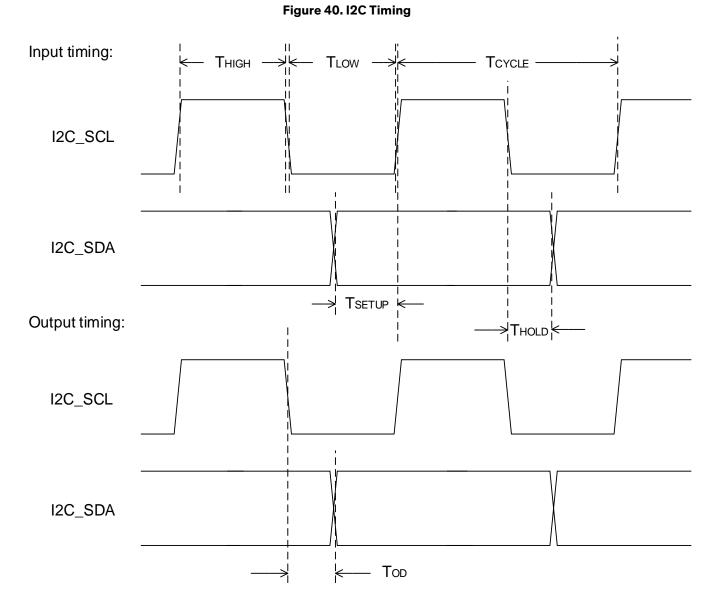

| 11.1 EQFP144 Package       130         11.2 FBGA256 Package       132         12. ORDERING INFORMATION       134         12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | 10.5.6 MDIO Timing                               |     |

| 11.2 FBGA256 Package       132 <b>12. ORDERING INFORMATION 134</b> 12.1 Part Ordering Numbers       134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11. | 1. MECHANICAL SPECIFICATION                      |     |

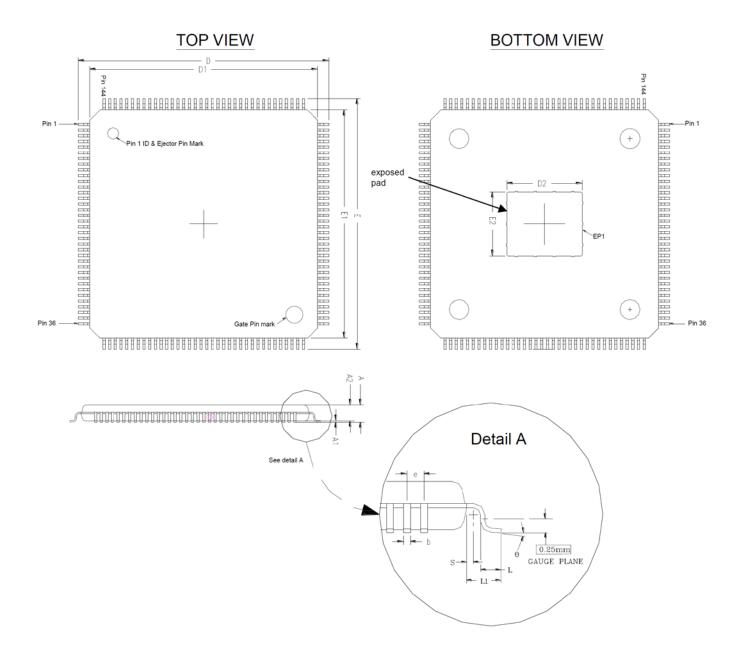

| 12. ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 11.1 EQFP144 Package                             |     |

| 12.1 Part Ordering Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 11.2 FBGA256 Package                             |     |

| 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12  | 2. ORDERING INFORMATION                          |     |

| 12.2 Sales Offices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 12.1 Part Ordering Numbers                       | 134 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 12.2 Sales Offices                               | 134 |

# Figures

| Figure 1. End-Node Application              | 9 |

|---------------------------------------------|---|

| Figure 2. RedBox Application                |   |

| Figure 3. Multiport RedBox Application      |   |

| Figure 4. QuadBox Application               |   |

| Figure 5. XRS7004E Device Pinout (Top View) |   |

| Figure 6. XRS7004F Device Pinout (Top View) |   |

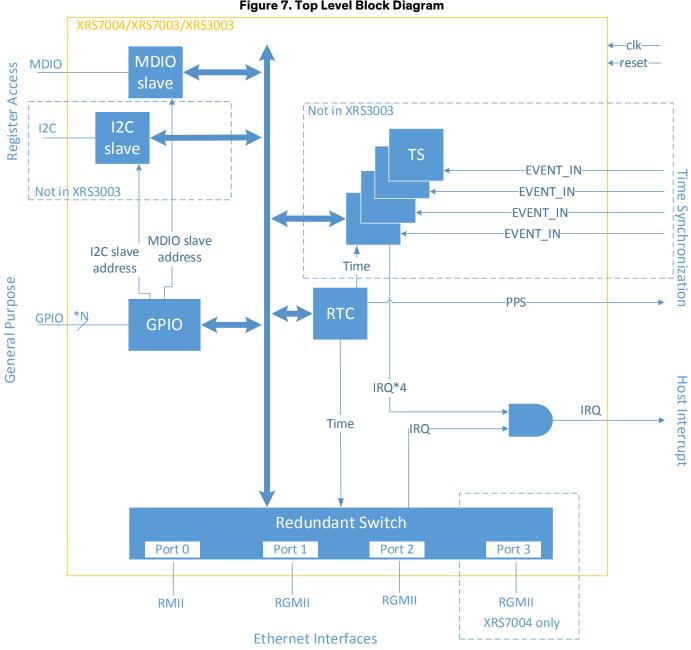

| Figure 7. Top Level Block Diagram           |   |

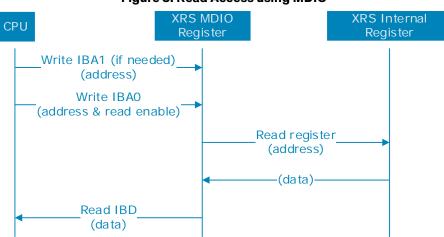

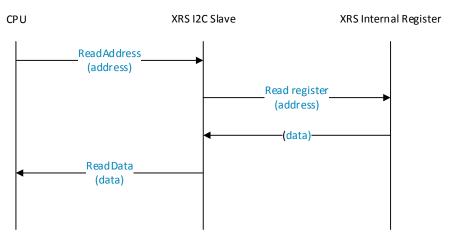

| Figure 8. Read Access using MDIO            |   |

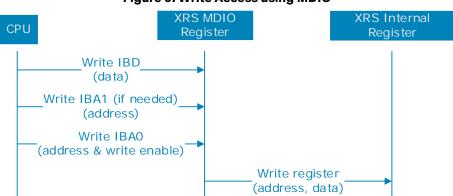

| Figure 9. Write Access using MDIO           |   |

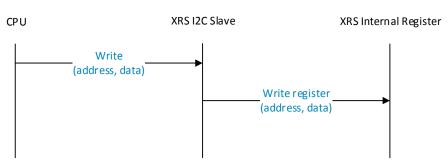

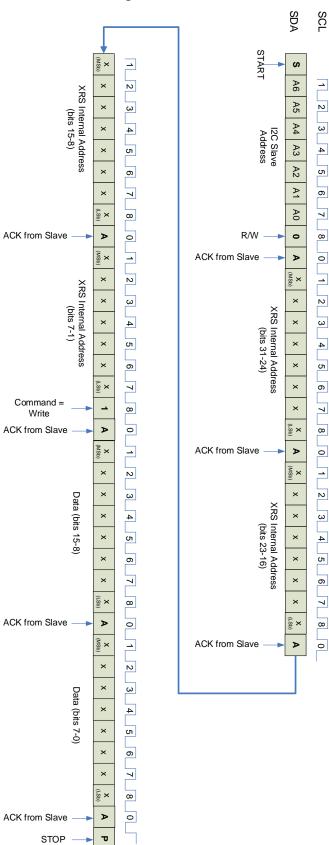

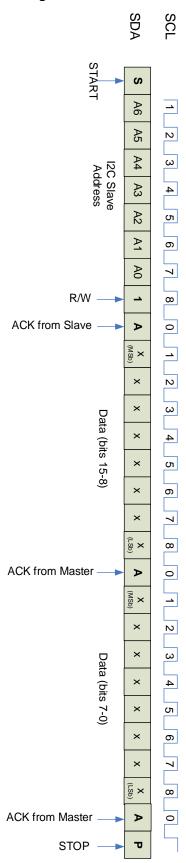

| Figure 10. Write Access using I2C           |   |

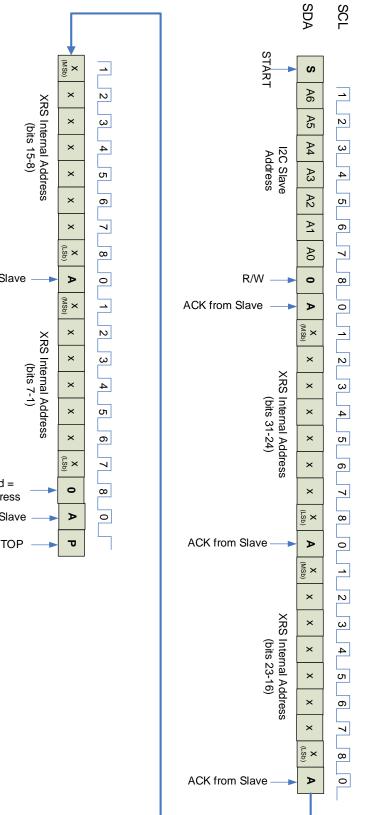

| Figure 11. Read Access using I2C            |   |

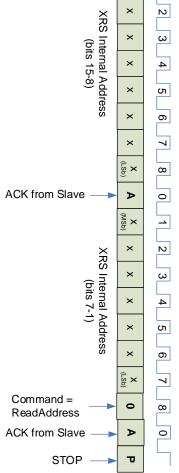

XRS7000 and XRS3000 User Manual, Version 1.3

V Five Years Out

| Figure 12. I2C Write                                               |     |

|--------------------------------------------------------------------|-----|

| Figure 13. I2C ReadAddress                                         |     |

| Figure 14. I2C ReadData                                            |     |

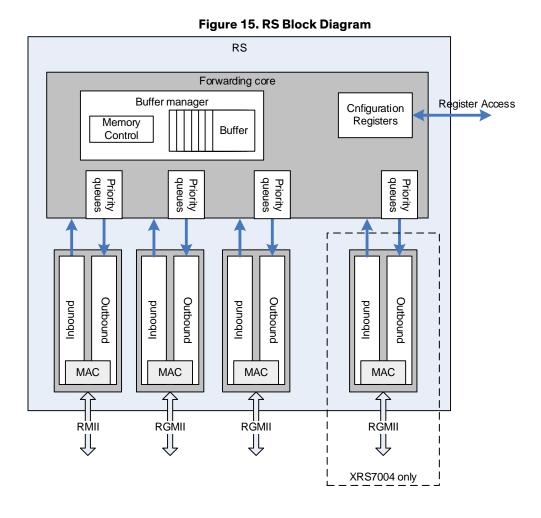

| Figure 15. RS Block Diagram                                        |     |

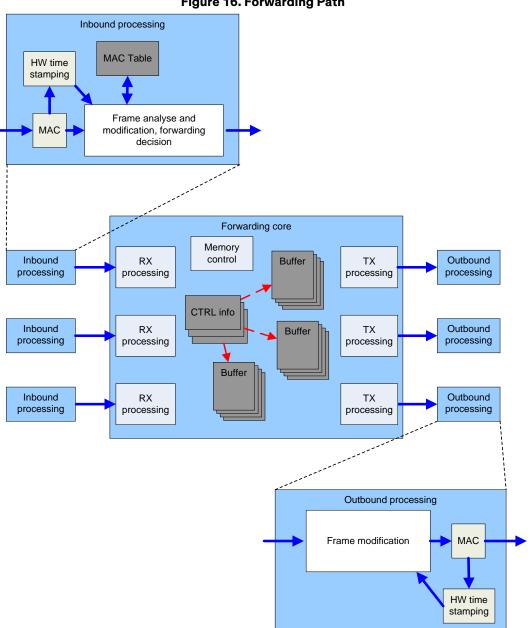

| Figure 16. Forwarding Path                                         |     |

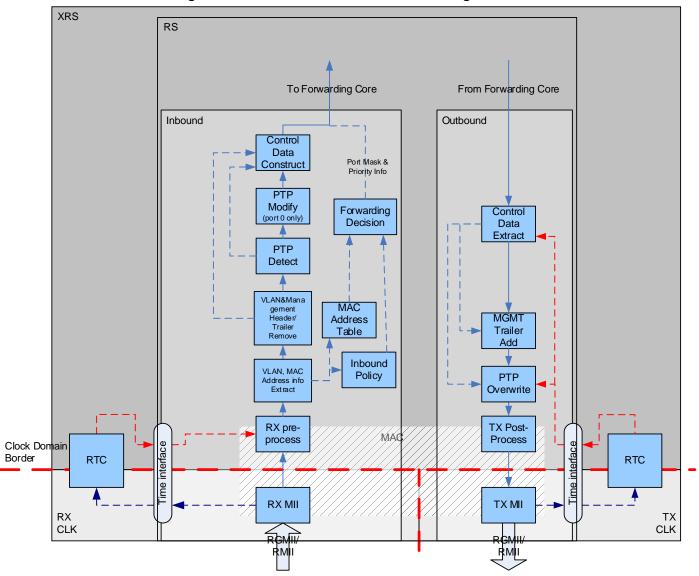

| Figure 17. RS Inbound and Outbound Processing Blocks               | 40  |

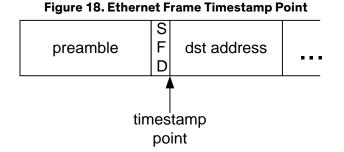

| Figure 18. Ethernet Frame Timestamp Point                          | 41  |

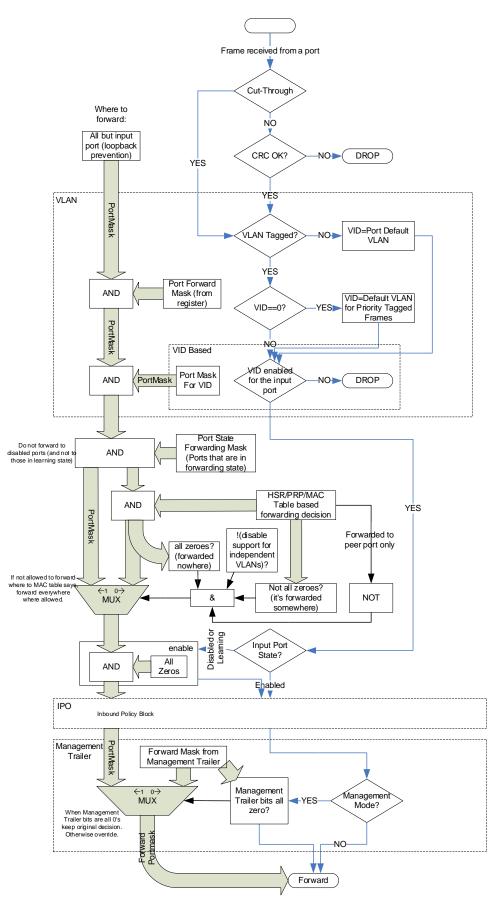

| Figure 19. Forwarding Decision                                     | 43  |

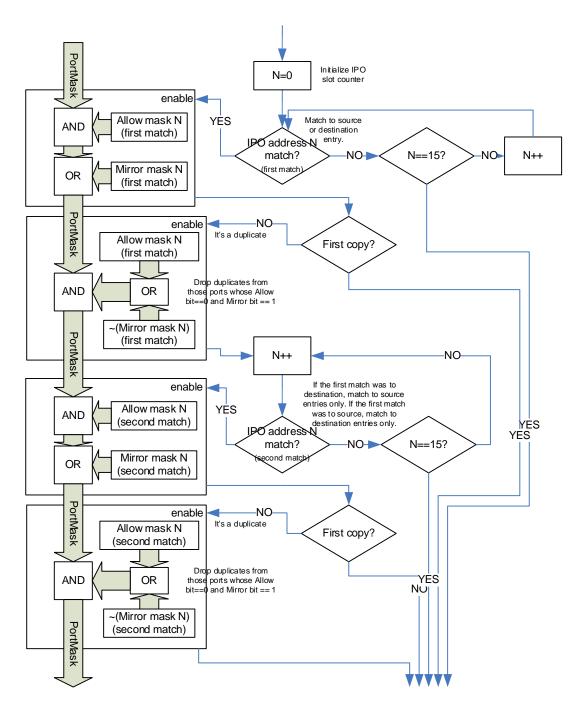

| Figure 20. Inbound Policy                                          | 45  |

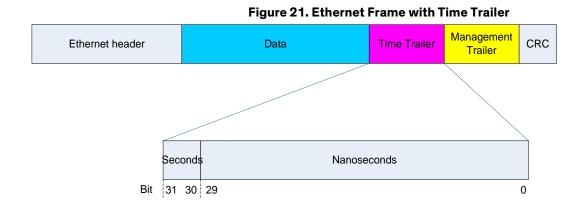

| Figure 21. Ethernet Frame with Time Trailer                        | 47  |

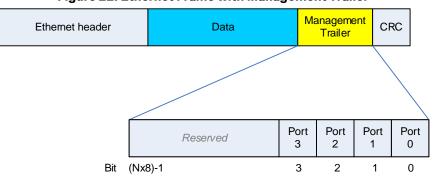

| Figure 22. Ethernet Frame with Management Trailer                  |     |

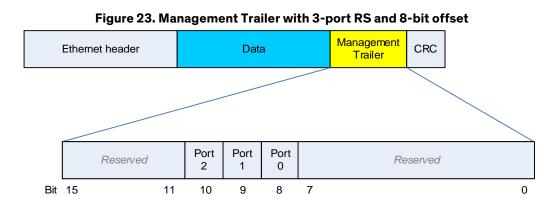

| Figure 23. Management Trailer with 3-port RS and 8-bit offset      |     |

| Figure 24. MAC Address Entry                                       |     |

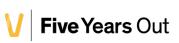

| Figure 25. Address Learning                                        | 51  |

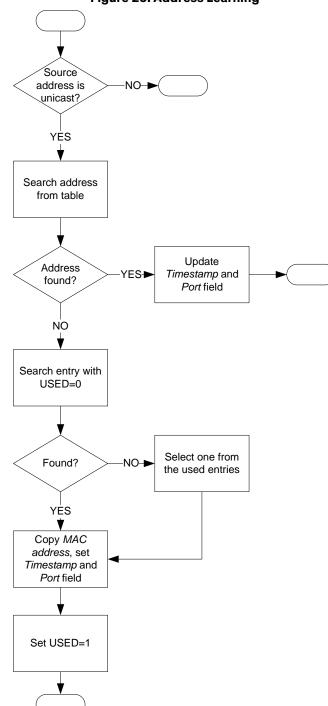

| Figure 26. Address Aging                                           |     |

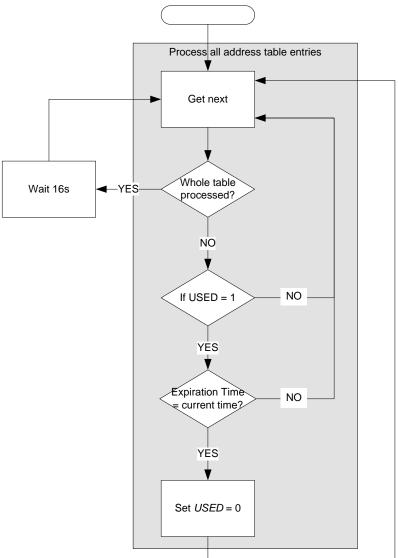

| Figure 27. MAC Address Search & Forwarding Decision                | 54  |

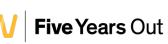

| Figure 28. Priority Queues (three ports shown)                     |     |

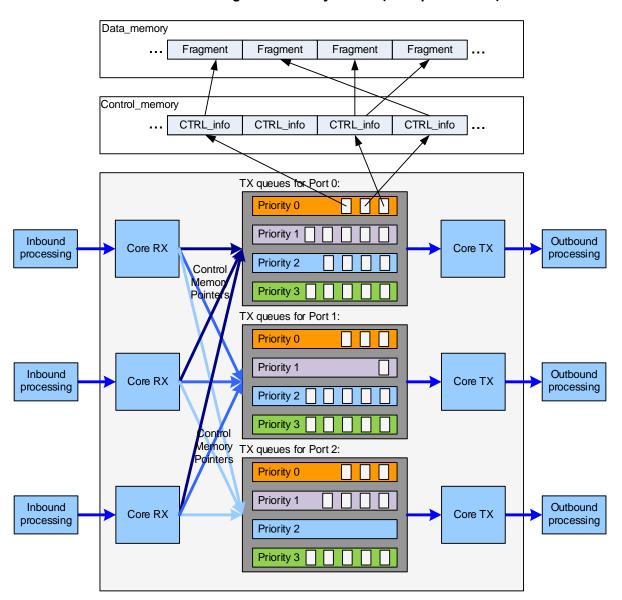

| Figure 29. Frame Early Drop Algorithm                              | 58  |

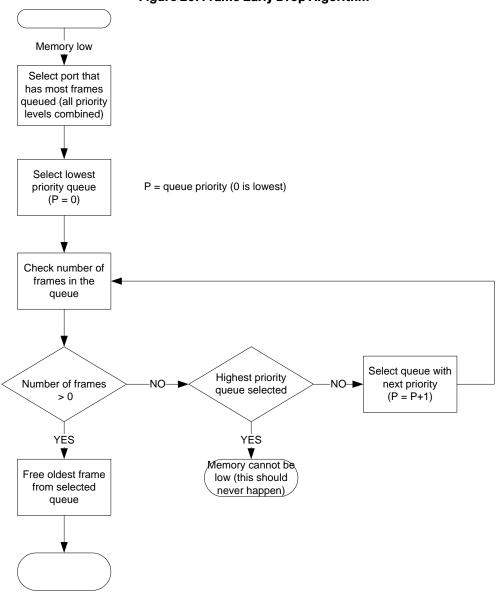

| Figure 30. Frame from normal port (or non-PRP frame from PRP port) | 59  |

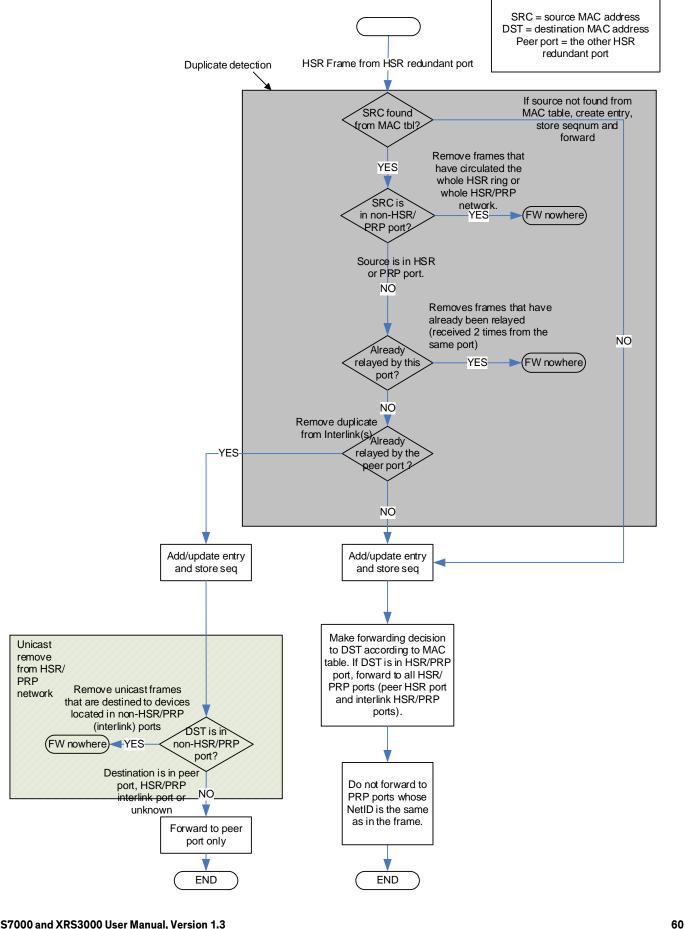

| Figure 31. HSR Redundant Port Forwarding Logic                     |     |

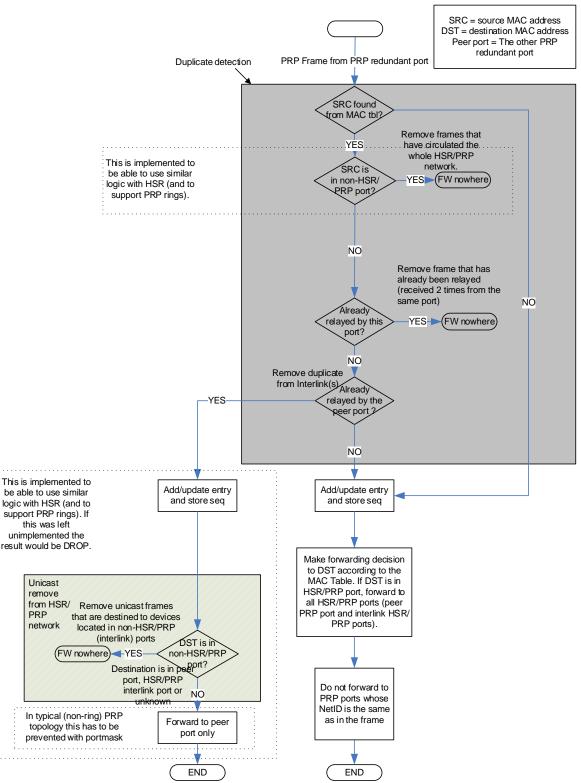

| Figure 32. PRP Redundant Port Forwarding Logic                     | 63  |

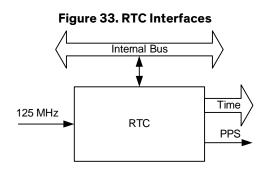

| Figure 33. RTC Interfaces                                          | 107 |

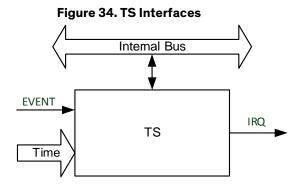

| Figure 34. TS Interfaces                                           | 112 |

| Figure 35. Reset Timing                                            | 124 |

| Figure 36. RGMII Timing                                            |     |

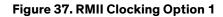

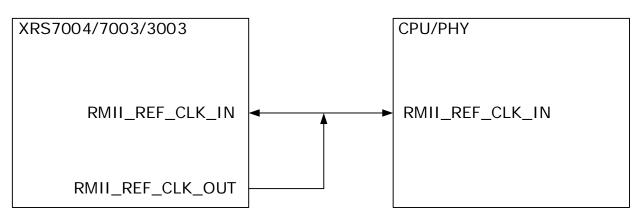

| Figure 37. RMII Clocking Option 1                                  |     |

| Figure 38. RMII Clocking Option 2                                  | 126 |

| Figure 39. RMII Timing                                             | 127 |

| Figure 40. I2C Timing                                              | 128 |

| Figure 41. MDIO Timing                                             |     |

| Figure 42. EQFP144 Package Dimensions                              | 131 |

| Figure 43. FBGA256 Package Dimensions                              | 133 |

# Tables

| Table 1. Device Features                                                                          |    |

|---------------------------------------------------------------------------------------------------|----|

| Table 2. Pin Types                                                                                | 12 |

| Table 3. EQFP144 Package RGMII Pin Definitions                                                    | 12 |

| Table 4. EQFP144 Package RMII Pin Definitions                                                     | 14 |

| Table 5. EQFP144 Package Register Access and Interrupt Pin Definitions                            | 14 |

| Table 6. EQFP144 Package Time Synchronization Pin Definitions                                     | 15 |

| Table 7. EQFP144 Package Clock and Reset Pin Definitions                                          | 15 |

| Table 8. EQFP144 Package Power and Ground Pin Definitions                                         |    |

| Table 9. EQFP144 Package Other Pin Definitions                                                    | 17 |

| Table 10. Pin Types                                                                               | 20 |

| Table 11. FBGA256 Package RGMII Pin Definitions<br>Table 12. FBGA256 Package RMII Pin Definitions | 20 |

| Table 12. FBGA256 Package RMII Pin Definitions                                                    | 21 |

| Table 13. FBGA256 Package Register Access and Interrupt Pin Definitions                           | 22 |

| Table 14. FBGA256 Package Time Synchronization Pin Definitions                                    | 22 |

| Table 15. FBGA256 Package Clock and Reset Pin Definitions                                         | 22 |

XRS7000 and XRS3000 User Manual, Version 1.3

| Table 16. FBGA256 Package Power and Ground Pin Definitions                                    |  |

|-----------------------------------------------------------------------------------------------|--|

| Table 17. FBGA256 Package Other Pin Definitions                                               |  |

| Table 18. Internal Register Map                                                               |  |

| Table 19. Identification Registers                                                            |  |

| Table 20. XRS MDIO Registers                                                                  |  |

| Table 21. MDIO Address                                                                        |  |

| Table 22. I2C Address                                                                         |  |

| Table 23. Definition of LanID, NetId, ring NetId and PathId                                   |  |

| Table 24. Resulting Lanld and NetId                                                           |  |

| Table 25. Allowed Port Modes                                                                  |  |

| Table 26. Switch Configuration Register Groups                                                |  |

| Table 27. General Switch Configuration Registers                                              |  |

| Table 28. Frame Timestamp Registers                                                           |  |

| Table 29. Virtual LAN Configuration Registers                                                 |  |

| Table 30. Port Configuration Register Groups                                                  |  |

| Table 31. General Configuration and State Registers                                           |  |

| Table 32. HSR Registers                                                                       |  |

| Table 33. Delay Correction Values for PTP Registers                                           |  |

| Table 34. PTP Registers                                                                       |  |

| Table 35. Counter Registers (not in XRS3003)                                                  |  |

| Table 36. Inbound Policy Registers                                                            |  |

| Table 37. RTC Registers                                                                       |  |

| Table 38. TS Registers (not in XRS3003)                                                       |  |

| Table 39. GPIO Block Register Map                                                             |  |

| Table 40. Absolute Maximum Ratings, EQFP144 Package                                           |  |

| Table 41. Absolute Maximum Ratings, FBGA256 Package                                           |  |

| Table 42. Recommended Operating Conditions, EQFP144 Package                                   |  |

| Table 43. Recommended Operating Conditions, FBGA256 Package                                   |  |

| Table 44. Thermal Resistance, EQFP144 Package                                                 |  |

| Table 45. Thermal Resistance, FBGA256 Package                                                 |  |

| Table 46. Current Consumption, XRS7004E                                                       |  |

| Table 47. Current Consumption, XRS7003E                                                       |  |

| Table 48. Current Consumption, XRS7004F                                                       |  |

| Table 49. Current Consumption, XRS7003F                                                       |  |

| Table 50. Current Consumption, XRS3003F                                                       |  |

| Table 51. I/O Characteristics, EQFP144 Package                                                |  |

| Table 52. I/O Characteristics, FBGA256 Package                                                |  |

| Table 53. Input Clock Timing (CLK)                                                            |  |

| Table 54. Reset Timing                                                                        |  |

| Table 55. RGMII Timing                                                                        |  |

| Table 56. RMII Timing                                                                         |  |

| Table 57. I2C Timing                                                                          |  |

| Table 58. MDIO Timing                                                                         |  |

| Table 59. EQFP144 Package Information                                                         |  |

| Table 60. EQFP144 Package Dimensions in Millimeters                                           |  |

| Table 60. EGT P 144 Package Dimensions in Minimeters<br>Table 61. FBGA256 Package Information |  |

| Table 62. FBGA256 Package Dimensions in Millimeters                                           |  |

| Table 62. PBGA250 Package Dimensions in Minimeters<br>Table 63. Part Ordering Numbers         |  |

|                                                                                               |  |

XRS7000 and XRS3000 User Manual, Version 1.3

V Five Years Out

# **Revision History**

| Rev | Date       | Comments                                                                                                                                                                                                                                               |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0 | 20.11.2015 | First release                                                                                                                                                                                                                                          |  |

| 1.1 | 15.4.2016  | XRS3003 and FBGA256 package added. JTAG interface removed.                                                                                                                                                                                             |  |

| 1.2 | 11.5.2016  | Interface timing changes:<br>- I2C input data setup time min changed from 0 ns to 50 ns<br>- RMII output delay max changed from 12 ns to 13 ns<br>- Power supply ramp time max changed from 50 ms to 3 ms<br>RGMII port indexes changed from 02 to 13. |  |

| 1.3 | 6.11.2017  | Added register bit for enabling/disabling support for independent VLANs. (Bit 7 in GENERAL register)                                                                                                                                                   |  |

Arrow Electronics Inc retains the right to make changes to this document at any time, without notice. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Arrow Electronics Inc makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purposes. Further, Arrow Electronics Inc does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Arrow Electronics Inc assumes no responsibility or liability whatsoever, and Arrow Electronics disclaims any express or implied warranty, relating use of Arrow Electronics Inc products liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Arrow Electronics Inc products are not intended for use in medical, lifesaving, life sustaining, critical control or safety systems, or in nuclear facility applications. Do not use Arrow Electronics Inc products in these types of equipment or applications.

XRS7000 and XRS3000 User Manual, Version 1.3

# **1. CONVENTIONS USED IN THIS DOCUMENT**

Signal names are written in this document with SignalName style. Block names are written with Capital first letter.

Register descriptions in this document follow these rules: Unless otherwise stated, all the bits that activate or enable something are active when their value is 1 and inactive when their value is 0. The explanation of register bit types is the following:

- RO = Read Capable Only. The bits marked with RO can be read. Writing to these bits is allowed unless otherwise stated. If writing is allowed, it does not affect the value of the bit.

- R/W = Read and Write capable. The bits can be read and written. Writing 1 to the bit makes its value 1.

Writing 0 to the bit makes its value 0.

- R/C = Read and Clear capable. The bits can be read and cleared. Writing 0 to the bit makes its value 0.

Writing 1 does nothing.

- R/SC = Read, Write and Self Clear. The bits can be read and written. Writing 0 to the bit does nothing.

Writing 1 to the bit makes its value 1 for a while, but after that the value automatically returns back to 0.

The bits marked as *Reserved* should not be written anything but 0, even if they are marked as read capable only, because their function may change in future versions.

XRS7000 and XRS3000 User Manual, Version 1.3

# **2. TYPICAL APPLICATIONS**

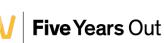

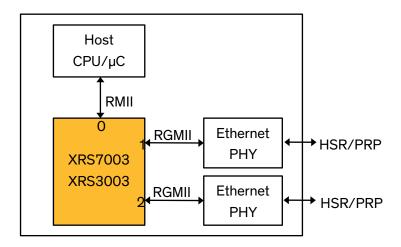

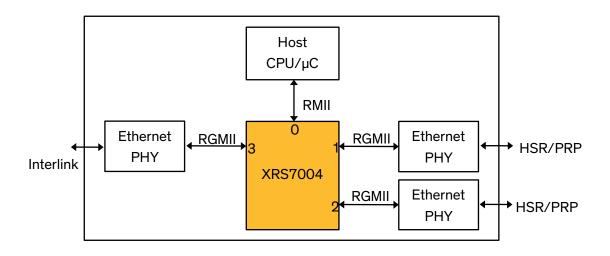

Typical applications for XRS7004, XRS7003 and XRS3003 are presented in Figure 1, Figure 2, Figure 3 and Figure 4.

Figure 1. End-Node Application

XRS7000 and XRS3000 User Manual, Version 1.3

Figure 3. Multiport RedBox Application

XRS7000 and XRS3000 User Manual, Version 1.3

## **3. PIN DESCRIPTION**

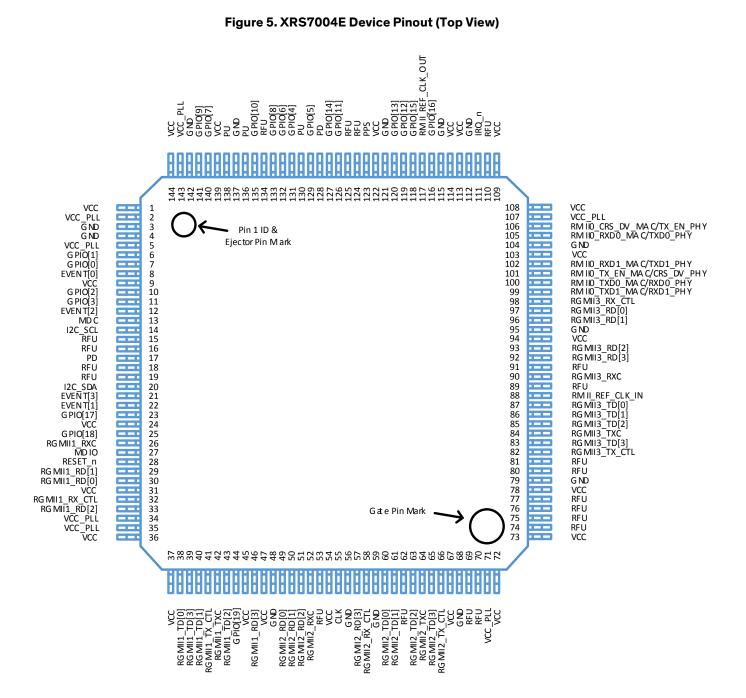

Devices are available in two different packages; XRS7004E and XRS7003E have EQFP144 package (Chapter 3.1) and XRS7004F, XRS7003F and XRS3003F have FBGA256 package (Chapter 3.2).

## 3.1 EQFP144 Package

Pin type definitions are listed in Table 2.

XRS7000 and XRS3000 User Manual, Version 1.3

| Table 2. Pin Types  |                                  |  |

|---------------------|----------------------------------|--|

| Pin type Definition |                                  |  |

| 1/0                 | Input and output                 |  |

| 1                   | Input only                       |  |

| 0                   | Output only                      |  |

| Power               | Operating power for the device   |  |

| Ground              | Ground connection for the device |  |

The pin definitions of XRS7004E (Figure 5) and XRS7003E are presented in the following tables (Table 3 to Table 9). Note that the only difference between the pinouts of XRS7004E and XRS7003E is that XRS7003E has two RGMII interfaces (RGMII1 and RGMII2) while XRS7004E has three RGMII interfaces (RGMII1, RGMII2 and RGMII3). At XRS7003E the RGMII3 input pins have internal pull-ups and RGMII3 output pins are driven low. At XRS7003 it is allowed to leave the RGMII3 input pins floating, drive them low or high or connect them to an RGMII interface of another chip.

Generally it is recommended to pull or tie all the unused input pins up or down unless otherwise stated in the Pin Description.

| Pin Number | Pin Name      | Pin Type | Pin Description                             |

|------------|---------------|----------|---------------------------------------------|

| 26         | RGMII1_RXC    | 1        | Receive Clock. The RX clock is 2.5 MHz for  |

| 52         | RGMII2_RXC    |          | 10 Mbit/s, 25 MHz for 100 Mbit/s and 125    |

| 90         | RGMII3_RXC    |          | MHz for 1000 Mbit/s.                        |

|            |               |          | Note that the PCB is required to add 1.5 ns |

|            |               |          | to 2.0 ns more delay to the clock line than |

|            |               |          | the other lines, unless the other end (PHY) |

|            |               |          | has configurable RX clock delay. See RGMII  |

|            |               |          | timing in Chapter 10.5.3.                   |

| 32         | RGMII1_RX_CTL | I        | Combined RXDV and RXER.                     |

| 58         | RGMII2_RX_CTL |          |                                             |

| 98         | RGMII3_RX_CTL |          |                                             |

| 30         | RGMII1_RD[0]  | I        | Receive Data. Double data rate at speed of  |

| 29         | RGMII1_RD[1]  |          | 1000 Mbit/s and single data rate at speeds  |

| 33         | RGMII1_RD[2]  |          | of 10/100 Mbit/s.                           |

| 46         | RGMII1_RD[3]  |          |                                             |

| 49         | RGMII2_RD[0]  |          |                                             |

| 50         | RGMII2_RD[1]  |          |                                             |

| 51         | RGMII2_RD[2]  |          |                                             |

| 57         | RGMII2_RD[3]  |          |                                             |

| 97         | RGMII3_RD[0]  |          |                                             |

| 96         | RGMII3_RD[1]  |          |                                             |

| 93         | RGMII3_RD[2]  |          |                                             |

| 92         | RGMII3_RD[3]  |          |                                             |

#### Table 3. EQFP144 Package RGMII Pin Definitions

| Pin Number                                                                 | Pin Name                                                                                                                                                                     | Pin Type | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42<br>64<br>84                                                             | RGMII1_TXC<br>RGMII2_TXC<br>RGMII3_TXC                                                                                                                                       | 0        | Transmit Clock. The TX clock is 2.5 MHz for<br>10 Mbit/s, 25 MHz for 100 Mbit/s and 125<br>MHz for 1000 Mbit/s.<br>Note that the <b>PCB is required to add 1.5 ns</b><br><b>to 2.0 ns more delay</b> to the clock line than<br>the other lines, unless the other end (PHY)<br>has configurable TX clock delay. See RGMII<br>timing in Chapter 10.5.3.<br>Note that the IO voltage is 3.3V and<br>therefore the other end has to be 3.3V<br>tolerant. |

| 41<br>66<br>82                                                             | RGMII1_TX_CTL<br>RGMII2_TX_CTL<br>RGMII3_TX_CTL                                                                                                                              | 0        | Combined TXEN and TXER.<br>Note that the IO voltage is 3.3V and<br>therefore the other end has to be 3.3V<br>tolerant.                                                                                                                                                                                                                                                                                                                               |

| 38<br>40<br>43<br>39<br>60<br>61<br>63<br>65<br>87<br>86<br>85<br>85<br>83 | RGMII1_TD[0]<br>RGMII1_TD[1]<br>RGMII1_TD[2]<br>RGMII2_TD[3]<br>RGMII2_TD[0]<br>RGMII2_TD[1]<br>RGMII2_TD[2]<br>RGMII3_TD[0]<br>RGMII3_TD[1]<br>RGMII3_TD[2]<br>RGMII3_TD[3] | 0        | Transmit Data. Double data rate at speed of<br>1000 Mbit/s and single data rate at speeds<br>of 10/100 Mbit/s.<br>Note that the IO voltage is 3.3V and<br>therefore the other end has to be 3.3V<br>tolerant.                                                                                                                                                                                                                                        |

XRS7000 and XRS3000 User Manual, Version 1.3

| Pin Number | Pin Name                   | Pin Type | Pin Description                             |

|------------|----------------------------|----------|---------------------------------------------|

| 105        | RMII0_RXD0_MAC/TXD0_PHY    | I        | RMII input data. In PHY mode this is        |

| 102        | RMII0_RXD1_MAC/TXD1_PHY    |          | transmit data. In MAC mode this is receive  |

|            |                            |          | data.                                       |

| 106        | RMIIO_CRS_DV_MAC/TX_EN_PHY |          | RMII input data valid. In PHY mode this is  |

|            |                            |          | TX_EN. In MAC mode this is CRS_DV.          |

| 100        | RMII0_TXD0_MAC/RXD0_PHY    | 0        | RMII output data. In PHY mode this is       |

| 99         | RMII0_TXD1_MAC/RXD1_PHY    |          | receive data. In MAC mode this is transmit  |

|            |                            |          | data.                                       |

| 101        | RMII0_TX_EN_MAC/CRS_DV_PHY | 0        | RMII output data valid. In PHY mode this is |

|            |                            |          | CRS_DV. In MAC mode this is TX_EN.          |

| 88         | RMII_REF_CLK_IN            | I        | RMII 50 MHz reference clock input. The      |

|            |                            |          | same reference clock must be used for the   |

|            |                            |          | both ends.                                  |

| 117        | RMII_REF_CLK_OUT           | 0        | 50 MHz reference clock output. Can be       |

|            |                            |          | connected to RMII_REF_CLK_IN or left        |

|            |                            |          | unconnected.                                |

#### Table 4. EQFP144 Package RMII Pin Definitions

Table 5. EQFP144 Package Register Access and Interrupt Pin Definitions

| Pin Number | Pin Name | Pin Type | Pin Description                               |

|------------|----------|----------|-----------------------------------------------|

| 13         | MDC      | 1        | Management Data Clock                         |

|            |          |          | If the interface is not used, the signal must |

|            |          |          | be pulled or tied up or down.                 |

| 27         | MDIO     | 1/0      | Management Data I/O. Must be externally       |

|            |          |          | pulled up. 10 k $\Omega$ pull-up resistor     |

|            |          |          | recommended.                                  |

| 14         | I2C_SCL  | I        | I2C clock                                     |

|            |          |          | If the interface is not used, the signal must |

|            |          |          | be pulled or tied up or down.                 |

| 20         | I2C_SDA  | I/O      | I2C data. Open drain. Must be externally      |

|            |          |          | pulled up. 10 k $\Omega$ pull-up resistor     |

|            |          |          | recommended.                                  |

| 111        | IRQ_n    | 0        | Interrupt Request Output. Active low, open    |

|            |          |          | drain. 10 k $\Omega$ pull-up resistor         |

|            |          |          | recommended.                                  |

XRS7000 and XRS3000 User Manual, Version 1.3

| Pin Number | Pin Name | Pin Type | Pin Description                               |

|------------|----------|----------|-----------------------------------------------|

| 8          | EVENT[0] | I        | Event Input. Time Stamper (TS, Chapter 8)     |

| 22         | EVENT[1] |          | can be used to time stamp the rising edges    |

| 12         | EVENT[2] |          | of the signal. Signals with frequency of 0 Hz |

| 21         | EVENT[3] |          | to 25 MHz are supported. Pull or tie unused   |

|            | L - J    |          | inputs up or down.                            |

| 123        | PPS      | 0        | Pulse Per Second output. A pulse with         |

|            |          |          | length of 20 $\mu$ s occurring once a second. |

|            |          |          | The rising edge of the pulse is when          |

|            |          |          | nanoseconds value of the RTC wraps            |

|            |          |          | around and the seconds value is               |

|            |          |          | incremented by one second.                    |

#### Table 6. EQFP144 Package Time Synchronization Pin Definitions

#### Table 7. EQFP144 Package Clock and Reset Pin Definitions

| Pin Number | Pin Name | Pin Type | Pin Description                   |

|------------|----------|----------|-----------------------------------|

| 55         | CLK      | 1        | 25 MHz reference clock input.     |

| 28         | RESET_n  | I        | Active low hardware reset signal. |

#### Table 8. EQFP144 Package Power and Ground Pin Definitions

| Pin Number | Pin Name | Pin Type | Pin Description                      |

|------------|----------|----------|--------------------------------------|

| 9          | VCC      | Power    | 3.3V operating power for the device. |

| 24         |          |          |                                      |

| 31         |          |          |                                      |

| 54         |          |          |                                      |

| 45         |          |          |                                      |

| 67         |          |          |                                      |

| 78         |          |          |                                      |

| 94         |          |          |                                      |

| 103        |          |          |                                      |

| 113        |          |          |                                      |

| 139        |          |          |                                      |

| 122        |          |          |                                      |